VOL. 210

DECEMBER 2014

기 1 → IDEC Newsletter I 통권 제210호

● 발행일 2014년 11월 30일● 발행인 박인철● 편집인 남병규● 제 작 푸울디자인

⊙기획전항기 ⊙전화 042) 350-8535 ⊙팩스 042) 350-8540 ⊙홈페이지 http://idec.or.kr

⊙ E-mail jhg0929@idec.or.kr ⊙ 발행처 반도체설계교육센터(IDEC)

반도체설계교육센터 사업은 미래창조과학부(산업통상자원부), 한국반도체산업협회, 반도체회사(삼성전자, SK하이닉스, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 에이티세미콘, TowerJazz)의 지원으로 수행되고 있습니다.

VOL. 210 DECEMBER 2014

# IDEC newsletter

## MPW (Multi-Project Wafer) 2014년 MPW 진행 현황

| 공정                   | 회차구분<br>(공정_년도순서) | 모집팀수<br>((mmxmm)x<br>칩수)/회별 | 정규모집<br>신청마감 | 참여팀수<br>((mmxmm))x<br>칩수)    | DB 마감<br>(Tape-out) | Die-out    | 비고   |

|----------------------|-------------------|-----------------------------|--------------|------------------------------|---------------------|------------|------|

| 삼성 65nm              | S65-1401          | (4x4)x48                    | 2013.12.09   | (4x4)x18                     | 2014.02.17          | 2014.08.18 | 제작완료 |

|                      | S65-1402          |                             | 2014.02.03   | (4x4)x37                     | 2014.08.25          | 2015.02.27 | 제작중  |

|                      | S65-1403          |                             | 2014.06.02   | (4x4)x30                     | 2014.12.15          | 2015.06.12 | 설계중  |

| 매그나칩/                | MS18-1401         |                             | 2013.12.09   | (3.8x3.8)x20                 | 2014.02.24          | 2014.07.28 | 제작완료 |

| SK하이닉스               | MS18-1402         | (2.0.2.0) 25                | 2014.01.06   | (3,8x3,8)x25                 | 2014.05.19          | 2014.10.20 | 제작완료 |

| 0.18 <i>µ</i> m      | MS18-1403         | (3.8x3.8)x25                | 2014.02.03   | (3.8x3.8)x21                 | 2014.08.11          | 2015.01.12 | 제작중  |

| 0,10                 | MS18-1404         |                             | 2014.05.05   | (3.8x3.8)x24                 | 2014.11.10          | 2015.04.13 | 제작중  |

| 매그나칩/                | MS35-1401         | (F () 00                    | 2014.01.06   | (5x4)x19                     | 2014.06.16          | 2014.10.06 | 제작완료 |

| SK하이닉스0.35μm         | MS35-1402         | (5x4)x20                    | 2014.06.02   | (5x4)x20                     | 2014.12.01          | 2015.03.23 | 설계중  |

| E H 0 44             | D11-1401          | (5,05),07                   | 2013.12.09   | (5x2.5)x22<br>(2,35x2,35)x4  | 2014.04.02          | 2014.08.06 | 제작완료 |

| 동부0.11 μm            | D11-1402          | (5x2,5)x24                  | 2014.04.07   | (5x2.5)x18<br>(2.35x2,35)x12 | 2014.10.01          | 2015.02.04 | 제작중  |

|                      | D18-1401          | (5x2.5)x4                   | 2013.12.09   | (5x2.5)x4                    | 2014.03.27          | 2014.07.02 | 제작완료 |

| ⊊ # 0.10 DOD         | D18-1402          |                             | 2013.12.09   | (5x2.5)x4                    | 2014.04.30          | 2014.08.06 | 제작완료 |

| 동부0.18μm BCD         | D18-1403          |                             | 2014.02.03   | (5x2,5)x2<br>(2,35x2,35)x4   | 2014.09.14          | 2015.1.10  | 제작중  |

|                      | D18-1404          |                             | 2014.05.05   | (5x2.5)x3<br>(2.35x2.35)x2   | 2014.11.05          | 2015.02.11 | 제작중  |

|                      | D35-1401          | (5x2.5)x6                   | 2013.12.09   | (5x2.5)x6                    | 2014.02.19          | 2014.05.28 | 제작완료 |

| 동부0.35#m BCD         | D35-1402          |                             | 2014.01.06   | (5x2.5)x2<br>(2.35x2.35)x7   | 2014.05.28          | 2014.09.03 | 제작완료 |

| <u>ら</u> 十0.30mm DCD | D35-1403          |                             | 2014.03.03   | (5x2.5)x4<br>(2.35x2.35)x4   | 2014.09.10          | 2014.12.17 | 제작중  |

|                      | D35-1404          |                             | 2014.05.05   | (5x2.5)x 5<br>(2.35x2.35)x2  | 2014.11.19          | 2015.02.25 | 제작중  |

| TowerJazz            | TJB18-1401        | (E. O E). /                 | 2014.01.06   | (5x5)x2<br>(5x2,5)x1         | 2014.05.12          | 2014.09.08 | 제작완료 |

| 0.18µm BCD           | TJB18-1402        | (5x2.5)x6                   | 2014.04.07   | (5x5)x2<br>(5x2.5)x2         | 2014.10.20          | 2015.02.16 | 제작중  |

| TowerJazz            | TJC18-1401        | (0.5.0.5)                   | 2014.01.06   | (2.5x2.5)x3                  | 2014.05.05          | 2014.09.01 | 제작완료 |

| 0.18µm CIS           | TJC18-1402        | (2,5x2,5)x4                 | 2014.04.07   | (2.5x2.5)x4                  | 2014.10.13          | 2015.02.09 | 제작중  |

| TowerJazz            | TJR18-1401        | (0 E.O E)/                  | 2014.01.06   | (5x2.5)x1<br>(2.5x2.5)x2     | 2014.06.23          | 2014.10.20 | 제작중  |

| 0.18µm CA18HA        | TJR18-1402        | (2.5x2,5)x4                 | 2014.04.07   | (2.5x2.5)x4                  | 2014.10.20          | 2015.02.16 | 제작중  |

| TowerJazz 0,18µmSiGe | TJS18-1401        | (2.5x2.5)x4                 | 2013.12.09   | (2.5x2.5)x4                  | 2014.03.11          | 2014.07.08 | 제작완료 |

\* 일정은 사정에 따라 다소 변경될 수 있음.

\* 회차 표기 방법 변경: 공정코드-년도 모집순서 (예시) 삼성65nm 2014년1회차:S65-1401)

\* Package 제작은 Die out 이후 1개월 소요됨

\* 기준일 : 2014.11.20.

\* 문의:이의숙 (042-350-4428, yslee@dec.or.kr)

## ○ 2014년 12월 교육프로그램 안내

수강을 원하는 분은 IDEC홈페이지(www.idec.or.kr)를 방문하여 신청하시기 바랍니다.

#### KAIST 개설 강좌 안내

| 센터명     | 강의일자        | 강의제목                                                   | 분류     |

|---------|-------------|--------------------------------------------------------|--------|

| 본센터     | 12월 1일-2일   | QuestaSim                                              | Tool강좌 |

| 근센니     | 12월 29일-30일 | 고성능 PLL 주파수 합성기 설계                                     | 설계강좌   |

| -101-11 | 12월 2일      | Scan Design and Its Application in Industry            | 세미나    |

| 한양대     | 12월 3일      | 자동차용 SoC 설계 방법론                                        | 세미나    |

| 광운대     | 12월 2일-3일   | Verilog HDL 이론 및 응용                                    | 설계     |

|         | 12월 4일-5일   | Verilog HDL 기초와 실습                                     | 설계     |

|         | 12월 22일-24일 | Full-custom 설계 입문                                      | 설계     |

| 충북대     | 12월 22일-27일 | Technical Skills on Technical Writing and Presentation | SoC분야  |

| =       | 12월 22일-27일 | Full Custom IC회로 설계(Tool사용법 실습강좌)                      | Tool강좌 |

강좌일: 12월 1일-2일강좌 제목: QuestaSim

• 강사 : Candice Zhao

**강좌개요** Digital Design Flow을 이해하고, Logic simulation 을 QuestaSim을 통하여 practical하게 습득하여, Design및 그의 Verification 능력 향상 **수강대상** HDL Design Engineer 또는 Verification Engineer

강의수준 초중급 강의형태 이론+실습 사전지식, 선수과목 Verilog와 Systemverilog의 이해

SoC Design 이해

• 강좌일 : 12월 29일-30일

• 강좌 제목 : 고성능 PLL 주파수 합성기 설계

• 강사 : 조성환 교수 (KAIST)

강좌개요 PLL의 기초와 원리를 이해하고 이를 집적회로로 응용한 고성능 주파수 합성기, 클럭 발진기 등에 대하여 알아본다.

수강대상 산업체 인력 및 대학원생

강의수준 중급 강의형태 이론+실습 사전지식, 선수과목

회로이론, 전자회로, 신호 및 시스템, 제어시스템, 랜덤 프로세스

\*문의: KAIST IDEC 오가영 (042-350-8536, oky0818@idec.or.kr)

• 강좌일 : 12월 2일 10:30~12:30

• 강좌 제목: Scan Design and Its Application in Industry

• 강사 : 천범익 박사 (ATsemicon)

강화개요 To meet the high test quality with low cost, full scan design technology has been applied in most SOC devices sine 1990s. Several issues of scan design in industry such as test time reduction, higher test quality, seamless design flow etc will be discussed in this lecture. We will also have an in-depth analysis of logic BIST and scan compression technology, most notably their applications which are practically adopted in industry.

VOL. 210 DECEMBER 2014

수강대상 학부생 석박사 일반인

강좌일: 12월 3일 15:00~17:00강좌 제목: 자동차용 SoC 설계 방법론

• 강사 : 공정택 교수 (한양대학교)

강좌개요 일반적인 SoC(System on Chip) 설계 방법론을 정리하고, 자동차용 SoC 설계 방법론과 비교한다. 특히, 자동차 기능 안전성 표준인 ISO 26262와 관련된 방법론을 소개한다. SoC 설계 툴을 제공하는 주요 EDA 회사 및 자동차용 반도체 회사들의 solution들과 기타 ISO 26262 지원 툴들을 소개한다. 마지막으로 자동차용 SoC 설계 대응 방안을 논한다.

수강대상 학부생, 석박사, 일반인

\*문의: 한양대 IDEC 오경주 (031-400-4079 , ipc@hanyang.ac.kr)

• 강좌일 : 12월 2일-3일

• 강좌 제목 : Verilog HDL 기초와 실습 • 강사 : 조경순 교수 (한국외국어대학교)

강좌개요 시스템 IC 분야에서 가장 널리 사용하는 하드웨어기술언어 Verilog HDL에 대한 기초와 이를 응용하여 회로를 설계하는 기법을 강의한다. 1995년 IEEE 1364-1995로 표준화된 Verilog HDL은 시스템 IC 설계 방법론의 가장 핵심적인 요소이다. Verilog HDL의 기초적인 문장에 대한 강의를 하고, synthesis를 고려한 코딩 기법에 대하여 강의한다. 기초 실습으로서 여러 가지 하드웨어 구성 요소에 대한 설계를 simulation 및 synthesis 실습을 통하여 진행한다. 수강대상 일반인/대학원생

**강의수준** 중급 **강의형태** 이론+실습

02

**U**3

12월 뉴스레터:레이아웃 1 14. 12. 15 오전 10:03 페이지 4

#### VOL. 210 DECEMBER 2014

## ○ 2014년 12월 교육프로그램 안내

• 강좌일 : 12월 4일-5일

• 강좌 제목 : Verilog HDL 이론 및 응용 • 강사 : 조경순 교수 (한국외국어대학교)

강좌개요 시스템 IC 분야에서 가장 널리 사용하는 하드웨어기술언어 Verilog HDL에 대한 이론과 이를 응용하여 회로를 설계하는 기법을 강의한다. Verilog HDL의 기본적인 문장들에 대해 살펴본 다음, 심화 내용으로서 non-determinism, non-blocking assignment 등을 concurrent process, simulation timing model과 같은 이론을 바탕으로 설명한다. 설계 실습으로서 영상압축 표준 JPEG의 DCT 모듈을 Verilog HDL을 이용하여 설계하고 검증한다.

수강대상 일반인/대학원생 **강의수준** 중급

강의형태 이론+실습

• 강좌일: 12월 22일-24일

• 강좌 제목 : Full-custom 설계 입문

• 강사 : 민경식 교수 (국민대학교)

#### 강좌개요

CMOS 회로 설계 tool을 이용한 CMOS 스케매틱 및 레이아웃 설계 방법을 배 운다. 이를 위해 Cadence Schematic Editor, Cadence Spectre, Cadence Layout Tool, Mentor DRC/LVS Tool의 사용법을 배우고 이를 사용한 스케매 틱 설계 및 검증, 레이아웃 및 레이아웃 검증에 관한 실습을 수행한다.

수강대상 일반인/대학원생 **강의수준** 중급 강의형태 이론 + 실습

\*문의: 광운대 IDEC 박아영 (02-940-5448, smartipc@kw.ac.kr)

• 강좌일 : 12월 22일-27일

• 강좌 제목: Technical Skills on Technical Writing and Presentation

• 강사 : 유영갑 명예교수 (충북대학교)

강좌개요 학위논문 기술문서 작성에 필요한 작문능력 배양을 위하여 작문기술 과 원리를 강의하고 실제 작문을 통하여 체득하게 한다. 기술발표를 위한 원고 작성 방법 및 프리젠테이션 방법을 훈련함.

수강대상 대학원 석 박사과정, 학부 4학년

• 강좌일 : 12월 22일-27일

• 강좌 제목 : Full Custom IC회로 설계(Tool사용법 실습강좌)

• 강사 : 양병도 부교수 (충북대학교)

강좌개요 Unix 기초 및 Cadence의 회로설계 Tool 사용법을 실습을 통하여

수강대상 학부생 및 석사과정생

**강의수준** 초급

강의형태 이론+실습

\*문의: 충북대 IDEC 캠퍼스 라해미 (043-261-3572, cbnu-idec@hbt.cbnu.ac.kr)

#### NDA가 체결된 Design Data 유출 금지 안내

IDEC의 MPW 참가를 통해 전달받은 Design Data 일 체는 NDA를 통해서 법적인 구속력을 가지며, 관리 소 홀로 인한 외부로의 공개 또는 유출 시 개인뿐만 아니 라 개인이 속해 있는 WG에 자격 박탈과 같은 강력한 규제가 가해질 수 있습니다. 협약에 의해, 형사상 책임 을 물을 수 있음을 알려 드립니다. MPW 참여자 분들 은 Design Data 및 관련 자료의 관리를 철저히 하시 어 불이익을 당하는 일이 없도록 거듭 당부 드립니다. NDA 체결 후 수령한 Design Kit 일체는 IDEC에 칩 수령 후 2개월 이내에 반드시 삭제하고 NDA 폐기확 인서를 제출하여 제3자에 의한 공개 및 유출이 일어나 지 않도록 주의 바랍니다.

KAIST에 위치한 반도체설계교육센터(IC Design Education Center, 이하 IDEC)는 한국의 주요 국공립대, 사립대 및 전문대에 VLSI 설계 교육, 칩 제조 서비스 제공을 위해 아날로그/ 믹스드 시그널(AMS) 및 EDA 소프 트웨어의 선도 기업인 실바코의 AMS 디자인 플로우를 도입하였다. IDEC은 대학의 VLSI 교육 및 연구 개발에 최신 정보와 소프트웨어를 제공하기 위하 여 항상 노력하고 있습니다. 실바코의 소프트웨어 제공을 통한 설계 환경 다 변화는, 다양한 설계 경험을 통해 설계 기술 과 능력 향상이 가능할 것이라 기대 됩니다. 실바코는 한국의 우수한 교육 시스템을 지원하기 위해 최선을 다하고 있습니다. 이번 IDEC과 SILVACO사의의 파트너십을 통하여, 한국 의 대학은 우수한 툴로 미래의 엔지니어들을 교육할 수 있게 되었으며, 이들 은 향후 실무에서 마주칠 과제에 대처할 수 있는 능력을 갖추게 될 것입니다."

- TS18SL (Mixed Signal CMOS 0.18um)

- TS18PM (Power Management 0.18um)

- TS18IS (CMOS image sensor 0.18um)

- CA18HD (CMOS 0.18um)

- SBC18HA (SiGe 0.18um)

#### 실바코 아날로그/믹스드 시그널 디자인 툴 소개

실바코의 아날로그/믹스드 시그널 디자인 툴 구성은 많이 사용하고 있는SmartSpice 회로 시뮬레이터, Gateway 스키매틱 에디터, Expert 레이아웃 에디 터, Guardian DRC/LVS/LPE,및 Hipex full-chip 기생 성분 추출 툴을 포함합니다. 실바코의 AMS 툴을 사용해서 IC 디자이너는 최적의 성능, 개발비 감 축. 위험 감소와 궁극적으로 TAT (turn around time)의 단축을 제공하는 반도체 제품을 만들 수 있습니다.

#### 실바코에서 제공하는 TowerJazz 프로세스 디자인 키트

IDEC에서 진행되고 있는 TowerJazz 공정에 적용 가능한 Silvaco 용 PDK를 지원한다고 발표 하였습니다. 멀티 프로세스 PDK는 교육 기관 및 팹리스 기업이 실바코의 IC 디자인 캡처, 시뮬레이션, 레이아웃 및 검증 도구를 이용하여 바로 설계및 제작을 용이하게 합니다.

IDEC(IC 설계 교육 센터)은 대학의 LSI 교육 및 연구 과정의 개발 진흥을 담 당하고 있습니다. IDEC은 칩 시험 제작 시스템을 구현 및 운영할 뿐만 아니 라, 대학 내 사용자들에게 최신 설계 툴 환경을 제공하고 있습니다. 또한, IDEC은 툴 및 최신 칩의 시험 제작에 대한 세미나를 정기적으로 개최하고 있습니다. 현재 한국에 있는 대학 대부분의 연구실에서 이용하고 있으며 연 간 320여 종류의 칩 제작 서비스를 지원하고 있습니다.

주소 대한민국 대전광역시 유성구 대학로 291(우: 305-701) 웹사이트 www.idec.or.kr

#### Silvaco, Inc.

Silvaco는 TCAD, 회로 시뮬레이션 및 IC CAD 소프트웨어 툴을 제공하는 선도 기업입니다. Silvaco의 툴은 반도체 공정을 개발하는 팹과 아날로그/믹 스드 시그널/RF 집적 회로를 개발하는 디자인 하우스에서 사용합니다. Silvaco는 서드-파티의 설계 플랫폼에 대한 인터페이스와 함께 완벽한 PDK 기반 설계 플로우를 제공합니다. Silvaco는 전세계 주요 지역에 사업 거점을 두고 있습니다.

• CEO David Halliday / david, halliday@silvaco, com

## IDEC inside1

# 시스템반도체 발전을 위한 선순환적 산·학협력 생태계 구축

세계반도체 시장규모는 2009년 2,317억 불에서 2013년 3,181억 불로 연평균 9%씩 꾸준히 성장했고 국내 반도체는 2013년에 515억 불을 생산하여 세계시장점유율 16.2%를 달성하여, 국내 반도체역사 최초로 세계 2위의 반도체 생산국이 되었다. 이중 메모리반도체 생산은 343억 불로 세계시장점유율이 52.4%이고, 시스템반도체 생산은 114억 불로 세계시장 점유율이 5.8%이다. 세계반도체 시장전망은 2013년 3,181억 불에서 2017년 3,859억 불로 연평균 5.3%씩 성장할 것으로 전망하고 있고, 이 중 메모리반도체는 2013년 655억 불에서 2017년 783억 불로 연평균 4.5%씩 성장할 것으로 전망하고 있다. 시스템반도체는 2013년 1,965억 불에서 2017년 2,369억 불로 연평균 5.1%씩 성장할 것으로 전망하다. 메모리반도체시장의 성장보다 시스템반도체시장의 성장을 좀 더 높게 보고 있다.

국내 시스템반도체산업은 아직 세계시장점유율이 미약하지만 많은 발전을 이룩했다. 2001년 국내의 시스템반도체가 세계시장에서 차지하는 비중이 불과 1.8%였으나, 2013년에는 5.8%로 지난 10년 동안 시장점유율이 3배 성장했고, 산업규모도 4배 이상 성장했다. 그동안 우리는 시스템반도체의 발전을 위하여 여러 가지 정책과 사업들을 추진했다. R&D의 경쟁력을 강화하기 위하여 1998년도부터 시작한 시스템 IC 2010 사업을 포함한 많은 R&D 사업들이 있었고, 기반을 강화하기 위한 시스템반도체산업지원사업, 그리고 인력을 양성하기 위하여 시스템반도체 인력양성사업, 반도체설계교육센터에서 주관하는 반도체설계인력양성사업 등을 추진했다. 그러한 결과로서 산업이 지금만큼 성장하였고, 스마트폰, 디지털 TV 등에서 사용되는 Application Processor, Micro Controller Unit, Display Driver IC, Power Management IC, CMOS Image Sensor 등 시스템반도체 중에서 핵심이 되는 반도체를 개발하여 세계시장에서 호평을 받고 있다. 앞으로 좀 더 많은 제품으로 세계시장에서 한국의 시스템반도체의 영역을 넓힐 것으로 기대하고 하고 있다. 그러나 우리는 지금 앞으로 시스템반도체의 발전을 위하여 해결해야 할 과제들을 고민해야 할 것이다. 지금까지와는 다른 환경에서 세계시장 점유율을 10% 이상 높여야 하는 새로운 목표를 달성해야 한다. 하지만 우리의 시스템반도체 성장에 대하여 많은 사람이 우려를 하고 있다. 미국, 유럽의 품질, 대만, 중국의 가격과 경쟁을 해야하는데 우리가 잘할 수 있는 이유를 찾기가 쉽지가 않다.

국내 시스템반도체산업의 구조는 삼성전자와 매그나칩과 같은 설계와 제조를 동시에 하는 종합반도체 기업과 SK하이닉스, 동부하이텍과 같은 제조를 전문으로 하는 파운드리 기업, 실리콘웍스, 실리콘마이터스, 실리콘화일 등과 같은 설계를 전문으로 하는 팹리스 기업 등으로 구성된다. 이러한 산업구조에서 국내 시스템반도체 성장에 가장 기여한 분야는 종합반도체 기업이고, 그 다음이 파운드리 기업이며 가장 성장이느린 분야가 팹리스 및 칩리스 기업이다. 이는 분야별 성장의 불균형이 문제로 지적되고 있다. 실제 미국, 대만 등 시스템반도체가 발전한 국가를 보면 설계전문기업과 제조기업이 균형적으로 발달되어 있고, 오히려 설계전문기업인 팹리스 기업의 성장이 더 높다. 우리도 팹리스 기업의 성장이 향후 국내 시스템반도체산업의 성장에 중요한 요인이 될 것으로 보고 있다. 우리는 1990년대 중반부터 지금까지 시스템반도체산업을 발전시키기 위하여 인력양성사업, 연구개발사업, 설계 Tool 지원사업, 시제품제작지원사업 등 많은 노력을 해왔다. 그래서 많은 인재가양성되었고, 세계 최고의 시스템반도체도 개발하여 글로벌 시장에 진출하는 등 많은 성과도 있었다. 그러나 경쟁은 상대적이었다. 미국과 같은 선발국과 대만, 중국과 같은 후발국은 우리보다 빨리 성장했다. 미국의 풍부한 인재, 시스템과 연계된 인프라, 대만과 중국의 전략적 성장지원은 우리가 생각했던 것보다 빠르게 시스템반도체산업을 발전시킨 것이다. 특히, 팹리스 기업의 발전은 '우리가 경쟁할 수 있을 것인가?' 할 정도로 발전되어 있다. 이러한 팹리스 기업의 성장에 가장 큰 문제로 지적되는 것은 IP와 SW로 대변되는 원천핵심기술과 인력의부족을 들고 있다. 국내 팹리스가 개발하는 시스템반도체의 내부 구성품 중 해외도입 비율은 50% 이상으로 추정한다. 이것이 개발기간을 늘리고, 제조원가를 높이며 제품을 다양화시키지 못하고 있다. 또한, 구매자로 하여금 구매동기를 저하한다. 현재 특허청의 지원으로 한국반도체산업협회 내에 시스템반도체개발에 필요한 IP를 원활하게 공급하기 위하여 반도체지적자산거래센서(KIPEX)가 운영되고 있지만, 아직도 사용할 수 있는 IP가 부족하다는 의견이 많다.

또 하나의 문제점은 인력부족이다. SW 및 SoC 관련 분야는 절대적으로 인력이 부족하며, 특히 설계 및 R&D 분야의 석·박사급 이상 고급 전문인력 부족은 심각하다. 대기업과 중소중견기업 모두 R&D 분야의 고급 전문인력 부족으로 기술역량 확보에 큰 어려움을 겪고 있다. 국내에서 배출되는 석·박사 반도체설계 전문인력은 연간 300명이 되지 않는다. 특히, 중소중견기업은 고급 전문인력 확보 측면에서 대기업과의 경쟁에서 밀리고 있어, 경쟁력 있는 기술개발에 한계가 있다. 각 대학의 관련학과 정원 축소로 향후 석·박사 인력의 신규 공급이 곤란하다. 이러한 인력문제를 해결하기 위하여 이미 1995년부터 반도체설계인력양성사업을 시작하여 산업의 성장에 많은 기여를 했다. 국내 시스템반도체 설계엔지니어 중에서 반도체설계교육센터를 거치지 않은 사람은 없을 정도였다. 그러나 이런 노력에도 불구하고 인력부족은 여전히 산업발전의 문제로 남아있고 오히려 더욱 심각해져 가고 있다고들 말하고 있다. 이런 환경에서 우리는 시스템반도체를 처음 시작했을 때 가졌던 문제점을 얼마나 해결했을까 하는 것과 지금까지와는 다른 방법이 필요하지 않을까 하는 것을 고민해야 한다. 옛날과 비교하면 지금은 세계 최고의 시스템반도체 제조시설을 갖추고 있고 글로벌시장에서 경쟁력을 갖춘 시스템반도체를 창출했으며 스마트폰, 디지털 TV 등 국내에 우리가 만든 시스템반도체를 사용하는 시스템산업이 발전되어 있다. 그러나 아직도 동일한 문제는 남아 있는 것이 있다. 시스템반도체를 개발할 때 사용하는 핵심 IP의 해외의존율과 인력의 부족이다.

핵심 IP의 국산화를 위하여 산업부와 특허청이 지원하고 한국반도체산업협회가 운영하는 반도체설계재산유통센터가 있지만, 유통의 기능에 머물러 있어서 IP를 창출하는 기능이 없다. 또한, 국내에 IP를 전문적으로 창출하는 기업이 아주 극소수이며 국내 시스템반도체 IP 시장이 아직은 협소하여 특정 IP를 제외하고는 기업의 사업영역으로서는 부족하다. 국내 산업구조에서 효율적인 IP 창출시스템이 필요하다. 인력의 부족은 영원한 숙제인 것처럼 문제의 단골메뉴로 등장한다. 이미 1995년에 반도체설계교육센터가 출범하여서 지금까지 유지가 되고 있고, 전자통신연구원도 시스템반도체 인력양성사업을 2004년부터 지금까지 추진하고 있다. 그러나 사업은 계속 축소되고 반도체를 지망하는 인력들은 점점 줄어들고 있다. 이런 현실은 10년 이상 문제로 고민하였고 나름대로 해결하기 위한 노력을 했다. 그러나 아직 여전히 문제로 남아 있다. 한 가지 부족하다고 생각한 것은 수요자와 공급자 간상호 이해와 대화인데, 이것이 부족하지 않았나 한다. 결국, 팹리스가 필요한 IP와 인력은 학교와 연구소로부터 나온다. 기업은 IP 개발이나 인력양성과정에서 학교나 연구소에 투자하지 않고 필요한 수요에 대해서도 요청이 없었다. 학교와 연구소는 나름의 기준으로 IP와 인력을 개발 및 양성하여 배출하였지만, 대다수가 잘 모르는 팹리스에 가기보다 인지도가 높은 대기업에 가기를 원한다. 바로 팹리스의 관심과 투자가 부족하지 않았나 하는 점을 고민해봐야 한다.

이를 해결하기 위해 지금보다 강한 그리고 시스템적으로 산학이 서로 대화할 수 있는 기구인 시스템반도체 산학협력 포럼이 얼마전 출범하였다. 이 포럼에서는 팹리스 기업이 필요한 IP를 산학이 공동을 개발할 수 있는 R&D를 추진하고자 하며, 기술분야별로 정기 기술포럼을 통한 산학 정보교류를 추진할 예정이며, 대학이 보유한 IP가 기업으로 확산할 수 있도록 Research IP Descovering를 정기적으로 개최할 예정이며, 중소·중견 팹리스 기업 우수인력 확보지원을 위한 각종 사업을 추진한다. 학교에서 개발된 우수기술이 창업으로 연결될 수 있도록 지원한다. 시스템반도체 설계인력 Job Fair 개최 (국제반도체대전, ISOCC 등과 연계), 공동 채용설명회 및 장학금 제도 운영하여 우수인력이 팹리스에 채용될 수 있도록 할 예정이다. 궁극적으로 시스템반도체 분야 산·학 협력 및 정보공유 강화로 산업을 성장시키고, 나아가 반도체산업에서 산·학이 동반 성장할 수 있는 새로운 협력모델을 구축하고, 타 분야로 확산하여 국내 산업발전에 새로운 산학협력모델로 발전시켜야 할 것이다. 이 포럼을 잘 활용하여 국내 팹리스가 발전하는데 도구로 사용하여야 할 것이다. 그러나 이를 위한 조건이 있다. 국내 팹리스가 이 포럼의 주인의식을 갖고 학교 및 연구소에 IP 개발과 인력양성을 위하여 투자해야 한다. 더는 정부 정책에 전적으로 의지한다면 우리에게 기회는 많지 않을 것이다.

#### \* 외부 필진 기고의 논조는 IDEC 방향과 다를 수 있습니다.

**안 기 현 본부장** 한국반도체산업협회

정전기(ESD: Electrostatic Discharge)는 EOS(Electrical Overstress)의 한 분류로써 일반 가정이나 사무실. 연 구소. 실험실 등 어느 장소에서나 일어날 수 있는 현상으로 각각 다른 전위를 갖는 두 물체 사이에서 마찰 전기에 의한 전하 이동 이다. 따라서 ESD는 매우 빠른 속도(~ns)로 어떤 상황에서든 발 생할 수 있는 현상으로 특히. 사람이나 전자 장비에서 ESD 현상 이 쉽게 발생한다. 이러한 ESD가 산업에 심각한 문제로 떠오르기 시작한 것은 한 세기 정도의 시간이 흘렀다. ESD를 방지하기 위 한 기술에 대한 최초의 기록은 1860년대라고 보고되었고, 이후 전자산업이 발달하면서 ESD 및 ESD와 관련된 새로운 문제들이 제기되었다. 오늘날 공정 기술의 발전과 더불어 IC의 고 집적화되 면서 ESD는 생산성과 상품의 안정성을 비롯해 전체적인 신뢰성 에 영향을 미치는 중요한 요인으로 작용하고 있다.

#### ESD에 의한 소자 파괴 분류 및 설계 영역

ESD에 의한 소자파괴 현상의 대부분은 크게 세 가지 ESD 모델 (HBM: Human Body Mode, MM: Machine Mode, CDM: Charge Device Model)에 의한 파괴로 다음과 같다. 접합영역에서 고 전류 및 전계에 의한 주울 발열과 높은 온도에 의한 2차 항복으 로 인한 소자파괴(HBM). 공정 기술이 발전함에 따른 게이트 산화막 두께가 얇아짐에 따른 높은 전계에 의한 산화막 파괴(CDM), 금속 배 선에 고전류가 흘러 취약 부분에 온도 상승으로 인해 배선이 얇아져 발생하는 금속 배선의 파괴(MM) 등이다. 각각의 모델은 ESD가 발 생하는 상황과 ESD의 공급원에 따라 분류된다 (표1).

| Model                              | НВМ                       | MM                                    | CDM Charged Device Model |  |

|------------------------------------|---------------------------|---------------------------------------|--------------------------|--|

| Wodei                              | Human Body Model          | Machine Model                         |                          |  |

| Origin                             | US Military<br>Late 1960s | Japan<br>1976                         | AT&T<br>1974             |  |

| RLC                                | 1.5kΩ,~8uH,100pF          | ~0Ω,~750nH,200pF                      | 1Ω,~1nH,1~20pF           |  |

| Peak Current                       | 1.33A<br>(@2000V)         | 2.8~3.5A<br>(@200V)                   | 8±1A<br>(@500V)          |  |

| Rising Time                        | 2~10ns                    | 15~30ns                               | < 1ns                    |  |

| Energy                             | Moderate                  | High                                  | Low                      |  |

| Bandwidth                          | 2.1M                      | 12M                                   | 1.1G                     |  |

| Basic Spec. for<br>Commercial IC's | +/- 2kV                   | +/- 200V                              | +/- 1kV                  |  |

| Super Spec.                        | +/- 10kV                  | +/- 1kV                               | +/- 2kV                  |  |

| Cause                              | Human Body                | Electro-statically<br>Charged Machine | IC Charge                |  |

표1. ESD Model 분류표

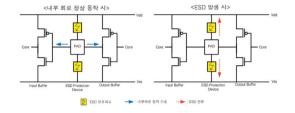

FSD 현상에 의한 반도체 소자의 피해를 막기 위해 IC의 제조환경이나 운반여건 등의 개선도 중요하지만, 가장 중요한 건 칩 내부에 ESD 보 호회로를 내장하여 ESD 발생 시 ESD 보호회로를 통해 내부 회로로의 유입을 방지하고 외부로 ESD를 방전시킬 수 있어야 한다. 그림 1은 ESD 보호회로의 개념을 나타낸다. ESD 보호회로는 정상적으로 회로 가 동작하는 상태와 ESD가 발생하는 상황을 정확히 구분되어 동작해 야 한다. 회로의 정상 동작 상태에서는 ESD 보호회로가 OFF 상태를 유지하여 내부 회로 동작에 영향을 미치지 않아야 한다. 반대로 ESD 발생 상황에서는 ESD 보호회로가 ON 상태를 유지하여 ESD 전류를 ESD 보호회로를 통하여 외부로 방출시켜야 한다. 이때 ESD 보호회로 는 설계영역(Design Window)이라 불리는 영역 내에서 동작해야 한다.

그림1. ESD 보호회로의 개념

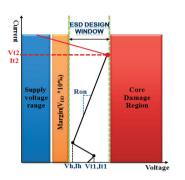

그림2. ESD 설계 영역

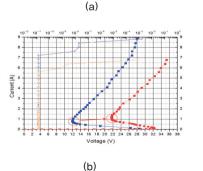

그림 2는 ESD 보호회로의 설계영역과 주요 파라메터를 나타낸 그 림이다. Vt1. lt1은 트리거 전압과 전류를 의미하여 ESD 보호회로 가 ON 상태가 되는 시점의 전압과 전류를 의미한다. 트리거 전압 은 내부회로에 사용된 일반 소자들의 항복을 일으키는 전압과 게이 트 산화막이 파괴되는 전압보다 작아야 한다. 포는 홀딩 전압을 뜻 하여 ESD 보호회로가 트리거 된 이후 ON 상태가 되었을 때 ESD 전류를 방전하는 동안에 보호회로 양단에 걸리는 최소 전압을 의미 한다. 정상 상태에서의 Latch-up 방지를 위해 홀딩 전압은 내부 회로의 동작전원 보다 커야 한다. Vt2, lt2는 2차 트리거 전압과 트 리거 전류를 의미한다. 2차 트리거 전압과 전류를 ESD 보호회로가 파괴되는 시점에서의 전압과 전류를 나타낸다.

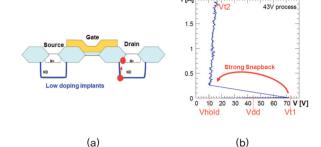

#### Power Clamp 단 ESD 보호회로 기술동향

일반적으로 고전압 소자가 요구되는 회로들이 많이 개발됨으로써 고전압 소자에 대한 관심이 커지게 되어 고전압 공정기술이 많이 개발되고 있다. 소자의 고 내압을 위한 낮은 도핑 레벨을 갖는 Implant와 두꺼운(Thick) 게이트 산화막을 갖추면 된다. 또한, 고신 뢰성을 위한 고전압 회로에서의 ESD 보호회로는 고내압을 위하여 고전압용 Implant와 게이트 산화막을 사용한다. 그러나 고내압을 위해 적용된 낮은 도핑 레벨의 Implant는 일반적인 ESD 보호회로 의 ESD 감내 특성뿐 만 아니라 고전류 상황에서의 동작을 감소시 키게 된다. 그림 3는 고전압 MOSFET의 단면도와 I-V특성을 나타 내고 있다. 고내압을 위해 사용되는 낮은 도핑 Implant(그림 3에서 의 ND)는 고전류 바이폴라 동작모드에서 Kirk effect의 효과로 강 한 Snapback 동작 효과를 가져온다. 그 이유는 초기 Avalanching 영역(Hot spot 영역)에 낮은 도핑으로 된 ND의 끝에 있다가 바이폴라 의 고전류 모드에서 Avalanching 영역이 높은 도핑으로 된 N+쪽으로 이동하여(그림 3에 빨간점)낮은 홀딩 전압을 갖게 되 었기 때문이다.

그림3. 고전압 MOSFET의 단면도 및 I-V 특성

이러한 특성으로 회로의 정상 동작 상태에서의 래치 업 문제가 발 생하게 된다. 이러한 원인으로 MOS 기반 고전압 ESD 보호회로인 고전압 MOSFET와 LDMOSFET은 래치 업 면역성이 떨어져 전체 시스템의 신뢰성이 약화 될 수 있다.

#### 고전압 Power Clamp용 ESD 보호회로의 설계 대책

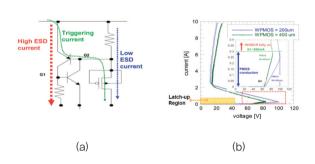

고전압 소자는 일반적으로 12V, 20V, 40V의 전원 전압을 사용하 는데 고전압 소자 또한 ESD에 대한 보호가 필요하다. 고전압 소자 를 ESD로부터 보호하기 위하여 고전압 클램프단 에 ESD 보호회 로가 내장되어야 하며 ESD 보호회로는 높은 신뢰성을 위하여 우 수한 ESD 감내 특성을 갖는 회로로 설계되어야 하며, 고전압 VDD 와 VSS 사이의 파워 클램프 단에 위치하기 때문에 회로의 정상 동 작 상태에서 래치 업 면역 특성이 좋은 높은 홀딩 전압과 홀딩 전 류를 갖는 ESD 보호회로가 설계 되어야 한다. 그림 4에서 높은 래 치 업 면역 특성을 갖는 PMOS Triggered SCR 파워 클램프 의 회로도 와 TLP I-V특성을 나타내었다.

그림4. (a) PMOS Triggered SCR Power Clamp의 회로도, (b) TLP I-V 특성

### 기술동향1

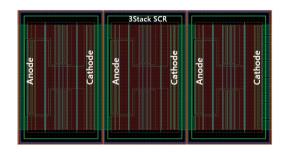

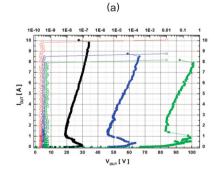

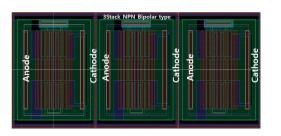

그림 4의 소자는 높은 감내 특성을 나타내는 SCR 소자를 기반으 로 설계되었으며, 정상 동작 상태에서의 래치 업 방지를 위하여 홀 딩 전류를 높인 소자이다. 일반적인 고전압 SCR에 트리거 소자로 PMOS가 사용되었다. 고전압 SCR은 약 150V 이상의 높은 항복 전압(PMOS Drain과 HV-Nwell)으로 Power IC 회로에 적용하기 어렵다. 그러나 고전압 PMOS를 사용하여 트리거 전압을 낮추었 다. 트리거 소자로 고전압 NMOS 대신 PMOS가 사용된 것은 고 전압 NMOS의 강한 Snapback 특성으로 래치 업 위험이 있고 소 자 신뢰성이 낮기 때문에 사용되었다. PMOS가 트리거 된 후 트리 거 전류는 증가하게 되어 G2 (PNP의 베이스) 노드의 전위를 높여 트리거 전류가 300mA 되었을 때 SCR이 동작하여 ESD 전류를 방전시키게 된다. PMOS의 의한 트리거 전류의 증가로 홀딩 전류 또한 증가하게 되어 정상 동작 상태에서의 래치 업 면역 특성을 증 가시켰다. 또한, 홀딩 전류의 증가뿐만 아니라 홀딩 전압을 전원 전 압보다 높게 하여 래치 업 특성을 향상시킨 기술도 있다. 대표적인 기술로 스택(Stack) 구조이다. 그림 5는 SCR 기반의 스택 기술은 NMOS 기반의 소자 면적보다 약 1/3의 면적 감소를 하는 효과와 약 두 배 이상의 감내 특성을 가진다. 그림 6은 BJT 기반 Power Clamp 용 ESD 보호회로를 나타낸다. BJT 기반 ESD 보호회로는 SCR 타입과 마찬가지로 스냅백 현상을 이용하지만 LDMSFET(Lateral Double Diffused MOSFET)과 같이 Double Diffused Drain 구조가 아니므로, 강한 스냅백 현상은 일어나지 않고, 이에 따라 LDMOSFET에 비해 상대적으로 높은 홀딩 전압 특성을 보인다. BJT 기반 ESD 보호회로는 SCR 기반 ESD 보호 회로에 비해 On-Resistance 및 높은 홀딩 전압 특성을 가진다. 또한, 스택 개수에 따라 홀딩 전압을 조절 가능하여 12V/20V뿐만 아니라 40V/ 60V급의 회로에도 적용할 수 있다.

그림 5. (a) Stacking SCR 구조, (b) TLP I-V 특성

(b)

(a)

그림6. (a) Stacking BJT 기반 ESD 보호회로 구조, (b) TLP I-V 특성

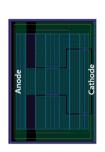

그림 7은 SCR 구조를 애노드 단의 P+와 캐소드 단의 N+를 분할하여 홀딩 전압을 높인 구조에 대한 그림이다. 애노드 단의 P+와 캐소드 단의 N+를 분할을 통하여 SCR 내의 기생 바이폴라 의 이미터 주입 효율을 낮춰 홀딩 전압을 12V에서 21V로 높였다.

Anode

⟨Conventional SCR⟩

$\langle Segmented SCR \rangle$

그림7. Segmented SCR의 (a) Layout, (b) TLP I-V 특성.

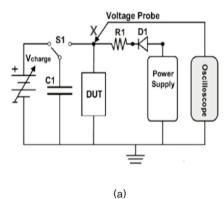

또한, 정확한 래치 업 면역성을 실험하기 위해 TLU(Transient-induced Latch-up) 실험을 한다. 그림 8(a)과 같이 DUT의 애노드 에 일정 전압으로 충전된 캐패시터를 이용하여 ESD 펄스를 재현함과 동시에 같은 노드 상에 내부 회로의 공급전압에 해당하는 DC 전압으로 설정된 전압 공급기를 연결한다. 이로써 내부 회로의 공급 전압이 ESD 보호회로에 공급되는 과정에서 스위치(S1)를 통해 캐패시터에 충전 전압이 인가(ESD 펄스 재현)되게 되면 ESD 보호회로가 동작 하게 된다. 이때 ESD 보호회로의 애노드에 해당하는 노드 X에서 전압 프로브를 이용하여 재현된 ESD 펄스에 의해 동작한 ESD 보호회로에 의해 DC 전압의 레벨 변화 유/무를 통해 래치 업이 발생했는지를 판단할 수 있다. 그림 8(b)은 TLU 측정을 통해 얻은 두 개의 전압 파형이다.

그림8. (a) TLU 측정 블록도 (b) 래치 업 발생(fail) (c) 래치 업 통과(pass)

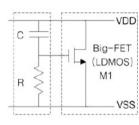

앞서 설명한 SCR 은 접합 항복을 통해 발생하는 전자와 정공을 통해 래치 모드로 동작하여 ESD 방전 경로를 형성하는 것과 달리 그림 9의 R-C 네트워크의 경우 소자의 외부에 달린 저항과 캐패시터의 시정 수(Time Constant)를 이용하여 150nsec 이내의 짧은시간을 갖는 ESD 펄스를 감지하고 이때 소자의 게이트 바이어스를 인가하여 소자의 턴-온 동작을 통해 ESD 방전 경로를 형성한다. 일반적인 ESD 보호회로들이 래치-모드를 통해 ESD 방전 경로를 형성하다. 일반적인 ESD 보호회로들이 래치-모드를 통해 ESD 방전 경로를 형성하기 때문에 스냅백 현상이 나타나게 되며 내부 회로의공급전압보다 낮은 홀딩전압을 갖게 될 경우 래치 업의 문제를야기할 수 있다. 하지만 R-C 네트워크를 통해 ESD 인가 시 스위치소자를 턴온 시키는 R-C 네트워크를 통해 ESD 인가 시 스위치소자를 턴온 시키는 R-C 네트워크를 병해 ESD 방전 경로를 형성하는 방식이 아니기 때문에 내부 회로 공급전압에 의한 래치 업이 발생하지 않는다. 이러한 R-C 네트워크를 이용한 ESD 보호회로들은 기존의 NMOS 또는 LDMOS를 통해 구성되고 연구되고 있다.

그림9. R-C 네트워크 ESD 보호회로

#### 결론

반도체 산업에서 공정 기술의 발전과 집적회로의 소형화 및 고 집 적화는 회로의 성능과 속도 향상을 가져왔지만, ESD 현상에 의한 회로의 오작동 및 파괴는 점점 심각한 문제로 인식되면서 면적 대비 높은 감내 특성, 빠른 트리거 속도, 높은 래치 업 면역 특성을 갖는 ESD 보호회로의 중요성이 커지고 있으며, 이러한 특성을 갖는 ESD 보호회로가 연구 개발되고 있다. 또한, 디스플레이 및 Power IC 회로는 전체 반도체 시장에 큰 영향을 끼치고 있으며 저면적/고성능/고신뢰성이 크게 요구되고 있다. 따라서 디스플레이 구동 회로 및 Power IC의 ESD 보호회로는 많은 입출력 핀 수와 패널 구동에 필요한 고전압 소자들을 고려하여 ESD 보호회로를 설계해야 한다. 높은 래치 업 면역 특성과 면적 대비 높은 감내 특성을 갖는 ESD 보호회로를 사용하여 ESD 보호회로를 구성한다면 디스플레이 및 Power IC 회로에서 요구하는 저 면적, 고신뢰성을 효과적으로 이룰 수 있을 것으로 사료 된다.

구 용 서 교수 소속: 단국대학교 전지전자공학부 연구분야: ESD 보호소자, Power Device, DC-DC converter yskoo@dankook.ac.kr http://user.dankook.ac.kr/~yskoo

12월 뉴스레터:레이아웃 1 14. 12. 15 오전 10:04 페이지 12

# SOI RF CMOS 소자 모델 라이브러리 구축

#### 1.서론

최근 이동통신용 단말기 시장이 급격히 신장되는 추세에 따라 제품 경쟁력을 확보하기 위해 고기능화 및 경박 단소화가 가장 중요한 기술 트랜드가 되고 있다. 이러한 트랜드에 가장 적합한 대안으로 단일 칩 내에 여러 가지 성능의 모듈 등을 내장시켜 시스템을 구성하는 실리콘 RF System on Chip(SoC) 공정 및 설계 기술이 중요하게 되었다.

이러한 RF SoC를 제조하기 위한 가장 적합한 실리콘 소자로서 최근 고저항 실리콘(HRS) SOI 기판을 사용하는 반도체 공정기술의 급격한 발달과 함께 RF Silicon-on-Insulator (SOI) CMOS 소자가 전 세계적으로 주목을 받고 있다 [1]. 그 이유는 SOI MOSFET이 bulk MOSFET에 비교해 RF 성능이 더 우수하기 때문이며, 이러한 장점은 근본적으로 소자 영역 아래에 위치한 buried oxide(BOX)층에 의해 집적회로 IC 내 소자들이 서로 분리되고 아래 실리콘 기판과도 연결되지 않은 절연 구조로부터 기인한다. 또한, 극히 낮은 RF dissipation 손실을 보여주는 HRS-SOI 기판의 사용으로 cross-coupling 및 cross-talk noise가 현저히 감소되어 RF SoC 제조에 매우 유리하다. 이와 같이 우수한 성능의 RF SOI SoC 설계를 위해서는 기본단위가 되는 RF SOI CMOS 소자의 정확하고 신뢰도 있는 SPICE 모델 [2] 라이브러리 개발이 매우 중요하게 대두하고 있다.

따라서 본고에서는 RF SOI CMOS 기술동향과 최근 나노종합기술 원의 연구비 지원으로 한국외국어대학교 RF 소자연구실에서 개발 한 SOI RF CMOS 모델 라이브러리 구축 기술에 대해 소개한다.

#### 2.기술 동향

상업적으로는 안정화된 공정을 기반으로 body contact partially depleted(PD)—SOI MOSFET이 일반적으로 사용되고 있으며 세계적으로 활발한 body contact (BCT) 구조 연구의 결과로 RF 성능지수인 cutoff frequency(fT)와 maximum frequency of oscillation(fmax)가 크게 향상되고 있다. 최근 0.13 $\mu$  m PD—SOI N—MOSFET 구조를 최적화하여 96.4GHz의 fT와 132.8GHz의 fmax를 보여주는 연구 결과가 발표되었다 [3]. SOI CMOS 수동 소자의 경우, 전 세계적으로 RF 시스템의 성능을 향상시키기 위해 더높은 quality—factor를 갖는 inductor와, 넓은 tuning range를 갖는 varactor, 단위 면적당 큰 캐패시턴스를 갖는 MIM 캐패시터및 낮은 오차의 저항 구조들을 개발하고 있다. 최근 연구로 2.73GHz에서 60의 quality—factor를 보여주는 HRS—SOI inductor 연구 결과가 발표되었다 [4]. 또한, HRS—SOI varactor를 사용하여 우수한 성능을 보여주는 40GHz의 voltage—controlled oscillator 설계 연구도 보고된 바 있다 [5].

모바일 단말기의 Front-End IC 응용분야에서 기존에는 성능이 우수한 GaAs와 같은 화합물 반도체소자가 RF Switch 제작에 사용되었으나 현재에는 SOI CMOS RF Switch에 대한연구가 큰 주목을 받고 있다. 이는 SOI CMOS 소자의 RF insertion loss가 bulk CMOS에 비해 크게 줄어들었고, 화합물반도체소자보다 dual 전압 조절이나 복잡한 주변회로가 필요 없어 회로가 단순하고 가격이 저렴하기 때문이다. 따라서 RF SOI CMOS 공정기술이 RF Switch 응용 IC 제작에 최적화되어있는 기술로 평가받고 있다.

최근 반도체 ASIC 파운드리(Foundry) 업체에서는 SOI CMOS 공정개발에 많은 투자를 집중하고 있다. 세계적으로 IBM과 Tower—Jazz에서는 이미 0.18 $\mu$  m SOI CMOS RF 공정기술을 보유하고 파운드리 서비스를 하고 있다. 또한, 국내 나노종합기술원에서도 0.18 $\mu$  m SOI RF CMOS 공정기술 개발을 2013년에 완료하고 최근 국내 매그나칩반도체에 기술이전을 진행하고 있는 상태이다. 이처럼 높은 RF 성능과 안정화된 공정을 바탕으로 향후 SOI CMOS RF 파운드리 서비스 시장은 크게 성장할 것으로 예상된다.

이러한 SOI 공정 서비스를 제공하기 위해서는 RF SOI CMOS 모델 라이브러리 구축을 통하여 process design kit (PDK) 환경을 확보하는 것이 중요하다. RF SOI CMOS 수동 소자의 경우, IBM에서 이미 저항, 캐패시터, Inductor, ESD 소자 및 패드 등의 RF모델 라이브러리를 파운드리 서비스로 제공하고 있다.

Short-channel SOI MOSFET RF 라이브러리 구축을 위한 SPICE 모델은 UC Berkeley와 IBM의 공동연구로 Berkeley short-channel IGFET model SOI 3 (BSIMSOI 3) [6]이 처음 개발되었다. 그 후에 DC 모델 시뮬레이션의 정확도를 증진시키고 RF 모델링이 가능하도록 개발된 BSIMSOI4 모델 [7]이 SOI CMOS IC 설계를 위한 세계적 표준 모델로 인정되어 상업화된 회로 시뮬레이터인 SPICE [8]에 일반적으로 사용되고 있다. 한편 RF Switching IC 응용분야에서는 Arizona State University와 NXP Semiconductors의 공동연구로 개발된 PSP-SOI 모델 [9]이 더적합한 모델로 인식되어 활발한 연구가 진행 중이다. RF 파운드리서비스로는 TowerJazz에서 PSP-SOI 모델 라이브러리를 제공하고 있고, IBM에서는 BSIMSOI 4와 PSP-SOI 모델 라이브러리를 함께 제공하고 있다.

하지만 original BSIMSOI4 모델은 BCT MOSFET에 맞는 scalable한 body 저항이 고려되지 않고 내부 캐패시턴스와 nonquasistatic 게이트 저항에 오차가 발생하여 개선이 필요하다. 이러한 문제점을 극복하기 위해서 기존 Bulk CMOS의 macro 모델링 방 법[10, 11]처럼 original BSIMSOI4 모델의 외부에 여러 lumped 성분들을 첨가하여 정확도를 개선한 macro 모델이 본 연구실에서 최근에 개발되었다.

#### 3. RF 모델 라이브러리

나노종합기술원의 SOI RF CMOS 공정으로 본 연구실에서 개발한 SOI 소자 RF 모델 라이브러리에는 다음과 같은 소자의 SPICE 모델들이 포함되어 있다.

#### ● 능동 소자

- 0.25μ m, 0.32μ m Tech BCT PD N/PMOSFET

#### ● 수동 소자

- 캐패시터: MIM, MOS Varactor

- 저항: High R, N+/P+ poly, N+/P+ diffusion, N-well

- Inductor: Standard, Symmetric, Symmetric with center tap

- ESD 다이오드 - RF 패드

ment group (TEG) 제작이 먼저 필요하다. 이때 RF TEG 패턴의 패드와 금속배선들의 기생성분들을 제거하는 de-embedding 용으로 사용하기 위해 open, short, through 테스트 패턴이 함께 제작된다 [12, 13]. 그 후에 제작된 RF TEG 패턴들의 측정된 S-파라미터를 사용하여 각 SOI CMOS 소자별로 scalable한 RF 모델개발이 수행된다. 이러한 SOI 소자 모델에서는 극히 낮은 RF dissipation 손실을 보여주는 HRS-SOI 기판의 사용으로 기판 손실이 거의 무시되므로 기존 bulk CMOS보다 훨씬 간단한 기판 등 가회로 구성이 가능하고 정확성도 증가시킬 수 있다.

이와 같은 SOI 능동 및 수동 소자의 RF 모델링을 위해서는

geometry를 다양하게 변화시킨 on-wafer RF 측정용 test ele-

이처럼 SOI CMOS 소자별로 수행된 RF 모델 라이브러리 구축 방법들을 설명하면 다음과 같다.

#### 1) SOI MOSFET 모델 구축

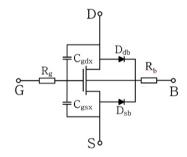

본 연구실에서는 Multi-finger RF BCT PD-SOI MOSFET의 RF 시뮬레이션 정확도를 개선하기 위해 그림 1처럼 기존의 original BSIMSOI4 모델을 수정한 Macro BSIMSOI4 모델을 개발하였다.

그림1. BSIMSOI4 RF Macro 모델

그림 1의 BSIMSOI4 모델에 연결된 macro element는 scalable 한 body 저항 [14]을 위한 Rb, non-quasi-static 효과 [15, 16] 를 위한 게이트 저항 Rg, 내부 캐패시턴스 모델 오차를 보정해 주기 위한 scalable 기생 캐패시턴스(Cgsx, Cgdx), multi-finger에 맞는 드레인 및 소스 junction 다이오드(Ddb, Dsb)로 구성된다. 이때 내부 드레인 및 소스 junction 다이오드를 없애기 위해 source/drain perimeter 길이를 PD=PS=0으로 놓는다.

## 7/술동향2

BSIMSOI4 모델 파라미터는 DC특성을 모델링하기 위한 DC 파라미터, AC와 transient 특성을 모델링하기 위한 캐패시턴스 파라미터와 RF macro 파라미터들로 나누어진다.

이러한 모델 파라미터는 다음과 같은 추출 기술을 사용하여 수행된다. 먼저 제작된 DC 및 CV TEG 패턴들을 사용하여 DC 및 CV 모델 파라미터들을 추출하고 그 후에 RF macro 파라미터들이 추출된다.

그림 1에서 외부에 첨가된 모든 RF Macro 파라미터들은 각각 직접 추출하기에는 복잡하므로, 100MHz에서 40GHz까지 multibias S-parameter optimization을 통해 정확히 추출하였다. 이 optimization 동안 추출된 BSIMSOI4 DC 및 캐패시턴스 모델 파라미터들은 상수로 고정된다. 특히 RF 비선형 특성을 정확히 모델 링하기 위해서는 넓은 bias point에서 측정된 여러 S-파라미터 set들과 동시에 잘 일치되도록 외부 macro 모델 파라미터를 optimization 하는 것이 중요하다.

이와 같은 optimization 방법으로 모든 TEG 패턴에서 추출된 SOI N/PMOSFET 소자의 게이트 길이(L), 단위 finger 폭 (Wu), finger 수(Nf) 종속 macro 파라미터 데이터들은 scalable 방정식으로 각 각 모델화된다.

#### 2) 저항 모델 구축

그림 2는 SOI RF 모델 라이브러리에 사용된 RF 저항 등가회로를 보여준다. 이 RF 모델은 RF 기판 분포 효과가 HRS-SOI 기판에 서 bulk Si 기판보다 훨씬 적기 때문에 2-section RLC 전송선로 등가회로로도 충분한 정확도를 달성할 수 있다. 또한, HRS-SOI 기 판 손실 효과가 매우 적기 때문에 기판 컨덕턴스는 제외하였다.

이러한 등가회로의 저항, 인덕턴스 및 캐패시턴스들은 RF TEG 패턴에서 S-parameter optimization을 통해 정확히 추출된다. 이때 추출된 R, L, C의 폭 (W)와 길이 (L) 종속 데이터들을 scalable 방정식으로 각각 모델화하여 N+/P+ diffusion, N+/P+ poly, N-well, High R 저항의 RF 모델 라이브러리가 구축되었다.

그림 2. RF 저항 등가회로 모델

#### 3) 캐패시터 모델 구축

#### 가. MIM 캐패시터

그림 3은 SOI RF 모델 라이브러리에 사용된 RF MIM 캐패시터 등 가회로를 보여준다. 초고주파 영역의 금속배선 효과를 고려하기 위해 직렬 인덕턴스와 저항이 추가되고 HRS-SOI 기판에 의한 손실 캐패시턴스를 모델화하기 위해 C와 Rbk가 직렬로 접지에 연결된다. 이때 MIM 캐패시터가 다른 소자들에 비해 Quality-factor가 매우 높기 때문에 정확한 모델링을 위해 Rbk가 포함된다.

그림 3. RF MIM 캐패시터 등가회로 모델

이러한 등가모델의 저항, 인덕턴스 및 캐패시턴스들은 S-parameter optimization을 통해 100MHz에서 self resonance frequency (SRF)까지 정확히 추출된다.

MIM 캐패시터의 RF 모델 라이브러리는 RF TEG 패턴으로 추출된 R, L, C의 W와 L 종속 데이터들을 scalable 방정식으로 각각 모 델화하여 구축되었다.

### 나. MOS Varactor

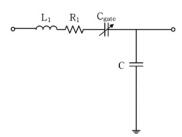

그림 4는 SOI RF 모델 라이브러리에 사용된 RF MOS varactor 등가회로를 보여준다. Cgate은 게이트와 body 사이의 MOS 캐패 시턴스이고, R1은 채널저항과 게이트 저항의 합을 나타낸다. C는 HRS-SOI 기판에 의한 캐패시턴스를 모델화하기 위해 접지에 연결된다. 이때 HRS 기판 손실효과가 매우 적기 때문에 기판 컨덕턴스는 포함하지 않았다.

MOS varactor 등가모델의 저항, 인덕턴스 및 캐패시턴스들은 100MHz에서 SRF까지 S-parameter optimization을 통해 정확히 추출된다.

이러한 S-parameter optimization으로 추출된 Cgate의 Vg 종 속 데이터들은 curve-fitting을 통해 bias 종속 비선형 Cgate 방 정식으로 모델화된다. MOS varactor의 RF 모델 라이브러리는 RF TEG 패턴에서 S-parameter optimization으로 추출된 R1, L1과 bias 종속 Cgate 파라미터들의 Nf, Wu와 L 종속 데이터들을 scalable 방정식으로 각각 모델화하여 구축되었다.

그림 4. RF MOS varactor 등가회로 모델

#### 4) Inductor 모델 구축

#### 가. Standard/Symmetric inductor

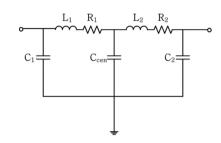

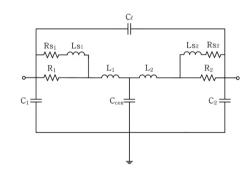

그림 5는 SOI RF 모델 라이브러리에 사용된 Standard/Symmetric spiral inductor 등가회로를 보여준다. R1, Rs1, R2와 Rs2는 metal의 직렬 저항이고 L1과 L2는 metal의 인덕턴스를 나타낸다. Ls1과 Ls2는 RF 영역의 metal skin effect 효과를 고려하기위해 추가된 인덕턴스이다. Cf는 spiral metal과 underpass metal 사이의 overlap 캐패시턴스 성분을 주로 나타낸다. C1, C2와 Ccen은 입력, 출력, 중앙 metal과 기판 사이의 병렬 캐패시턴스를 나타낸다. 이 모델은 HRS-SOI 기판효과가 매우 적기 때문에 bulk CMOS inductor 모델 [17]에서 기판 컨덕턴스를 제외한 등가회로이다.

그림 5. Standard와 Symmetric inductor 등가회로 모델

이러한 등가모델의 저항, 인덕턴스 및 캐패시턴스들은 100MHz에서 SRF까지 S-parameter optimization을 통해 정확히 추출된다.

Standard와 Symmetric inductor의 RF 모델 라이브러리는 RF TEG 패턴에서 추출된 R, L, C의 outer diameter(D), turn 수(Nt), turn 폭(W) 종속 데이터들을 scalable 방정식으로 각각 모델화하여 구축되었다.

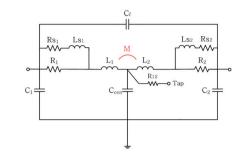

#### 나. Symmetric inductor with center tap

그림 6은 SOI RF 모델 라이브러리에 사용된 Symmetric spiral inductor with center tap 등가회로를 보여준다. L1과 L2는 metal의 mutual coupling coefficient k를 가진 상호 인덕턴스 M을 나타내고, R12는 center tap metal의 저항을 나타낸다. 등가모델의 저항, 인덕턴스 및 캐패시턴스들은 100MHz에서 SRF 까지 S-parameter optimization을 통해 정확히 추출된다.

그림 6. Symmetric inductor with center tap 등가회로 모델

Symmetric spiral inductor with center tap의 RF 모델 라이브 러리는 RF TEG 패턴에서 추출된 R, L, C의 D, Nt, W 종속 데이 터들을 scalable 방정식으로 각각 모델화하여 구축되었다.

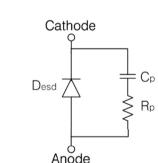

#### 5) ESD 다이오드 모델 구축

그림 7은 SOI RF 모델 라이브러리에 사용된 poly contact 된 N+/Pwell과 P+/Nwell ESD 다이오드의 RF 등가회로를 보여준다. Desd는 다이오드 모델이고, Rp는 poly 저항성분이고 Cp는 N+/P+영역과 poly 사이의 overlap 캐패시턴스 성분을 나타낸다.

SPICE 다이오드 DC 모델의 forward와 reverse bias parameter들은 각각 측정된 I-V 특성 곡선들과 동시에 일치되도록 curve-fitting을 수행하여 추출된다. SPICE 다이오드의 캐패시턴 스 모델 parameter는 측정한 C-V 곡선을 curve-fitting하여 추출된다. 이렇게 추출된 캐패시턴스 모델 parameter와 다이오드의 직렬저항이 RF 영역에서 정확한지 검증하고 Rp 값을 추출하기 위해서 측정된 S-파라미터 데이터와 일치되도록 RF optimization이소해되다.

그림 7. ESD 다이오드 등가회로 모델

3

SOI RF CMOS 소자 모델 라이브러리 구축

12월 뉴스레터:레이아웃 1 14. 12. 15 오전 10:04 페이지 16

#### 6) RF 패드 모델 구축

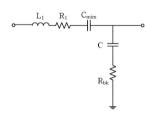

그림 8은 SOI RF 모델 라이브러리에 사용된 RF 패드의 등가회로를 보여준다. HRS-SOI 기판에 의한 손실 캐패시턴스를 모델화하기 위해 접지에 C와 R이 직렬로 연결된다. 이때 다른 소자들에 비해 큰 C성분 때문에 정확한 RF 모델링을 위해 R이 포함되었다

이러한 등가모델의 C와 R은 100MHz에서 40GHz 까지 S-parameter optimization을 통해 정확히 추 출된다.

RF 패드의 모델 라이브러리는 RF TEG 패턴에서 추출된 C와 R의 W 및 L 종속 데이터들을 scalable 방정식으로 각각 모델화하여 구축되었다.

그림 8. RF 패드의 등가회로 모델

#### 4. 결론

최근 RF Front-End IC를 제조하기 위한 가장 적합한 소자로서 RF SOI CMOS 소자가 전 세계적으로 주목을 받고 있으며, 이에 따라 RF SOI CMOS SPICE 모델 라이브러리 구축 연구가 매우 중요하게 대두하고 있다. 따라서 본고에서는 관련 기술동향을 요약하고 최근 본 연구실에서 개발한 SOI RF CMOS 수동 및 능동소자 모델 라이브러리 구축 기술에 대해 자세히 설명하였다.

이 성 현 교수 소속 : 한국외국어대학교 전자공학과 연구분야: CMOS 및 바이폴라 소자 모델링

#### 참고문헌

[1] K. B. Ali, C. R. Neve, A. Gharsallah, and J.-P. Raskin, "RF Performance of SOI CMOS Technology on Commercial 200-mm Enhanced Signal Integrity High Resistivity SOI Substrate," IEEE Trans. Electron Device, vol. 61, no. 3, pp. 722-728, 2014.

[2] SPICE Models Manual, SILVACO Inc, Santa Clara, CA, 2012.

[3] K. Lu, J. Chen, J. Luo, J. Liu, Q. Wu, Z. Chai, and X. Wang, "Improvement of RF performance by using tunnel diode body contact structure in PD SOI nMOSFETs," IEEE Electron Device Lett., vol. 35, no. 1, pp. 15-17, Jan. 2014.

[4] B. A. Ali, C. R. Neve, Y. Shim, M. Rais-Zadeh, and J.-P. Raskin, "Non-linear characteristics of passive elements on trap-rich high-resistivity Si substrates," in Proc. IEEE 14th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst., Newport Beach, CA, USA, Jan. 2014, pp. 4-6.

[5] N. Fong, J. Kim, J.-O. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C. Plett, and G. Tarr, "A low-voltage 40-GHz complementary VCO with 15% frequency tuning range in SOI CMOS technology," IEEE J. Solid-State Circuits, vol. 39, no. 5, pp. 841-846, 2004.

[6] BSIMSOIv3.0 MOSFET MODEL Users'Manual, Department of Electrical Engineering and Computer Science, University of California, Berkeley, 2002.

[7] BSIMSOIv4.4 MOSFET MODEL Users'Manual, Department of Electrical Engineering and Computer Science, University of California, Berkeley, 2010.

[8] SmartSpice User's Manual, SILVACO Inc, Santa Clara, CA, 2012.

[9] W. Wu, X. Li, G. Gildenblat, G.O. Workman, S. Veeraraghavan, C.C. McAndrew, R. van Langevelde, G.D.J. Smit, A.J. Scholten, D.B.M. Klaassen, J. Watts, "PSP-SOI: An advanced surface potential based compact model of partially depleted SOI MOSFETs for circuit simulations", Solid-State Electronics, vol. 53, pp. 18-29, 2009.

[10] 차지용, 차준영, 이성현, "Wide Width Effect를 고려하여 개선된 SPICE MOSFET RF Model 연구"전자공학회 논문지 제 45권 SD편 제 2호, pp. 7-12, 2008.

[11] 이현준, 이성현, "RF MOSFET을 위한 SPICE 기판 모델의 스케일링 정확도 분석"전자 공학회 논문지 제 49권 제 12호, pp. 173-178, 2012.

[12] J. Cha, J. Cha, and S. Lee, "Uncertainty analysis of two-step and three-step methods for deembedding on-wafer RF transistor measurements," IEEE Trans. Electron Device, vol. 55, pp. 2195-2201, 2008.

[13] J.-Y. Kim, M.-K. Choi, and S. Lee, "A Thru-Short-Open De-embedding Method for Accurate On-Wafer RF Measurements of Nano-Scale MOSFETs," Journal of Semiconductor Technology and Science, vol. 12, no. 1, pp. 53-58, 2012.

[14] J. Han and H. Shin, "A scalable model for the substrate resistance in multi-finger RF MOSFETs," in IEEE MTT-S Int. Microwave Symp. Dig., pp. 2105-2108, 2003.

[15] S. Lee and H. K. Yu, "Determining non-quasi-static small-signal equivalent circuit of a RF silicon MOSFET," Solid State Electronics, vol. 45, pp. 359-364, 2001.

[16] H.-J. Lee and S. Lee, "A new extraction method for non-quasi-static gate resistance of RF MOSFETs," Electron. Lett., vol. 48, no. 23, pp. 1501-1503, 2012.

[17] F. Huang, J. Lu, N. Jiang, X. Zhang, W.Wu, and Y.Wang, "Frequency independent asymmetric double-# equivalent circuit for on-chip spiral inductors: Physics-based modeling and parameter extraction," IEEE J. Solid-State Circuits, vol. 41, no. 10, pp. 2272-2283, Oct. 2006.--

15

SOI RF CMOS 소자 모델 라이브러리 구축

# Mentory Board Station

A. 목적 Circuit and PCB Design

B. 구분 회로 및 PCB 설계 Solution을 제공

C. Supported Platform and O/S System

- Linux RHEL 4, 532/64bit

- Linux SLES 10 32/64bit

- Solaris 10 UltraSPARC

- Windows 7 32/64bit, XP 32Bit, Server 200832/64bit, Server2003 32bit, Vista 32/64bit

#### D. 특성 및 기능

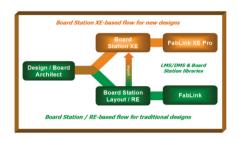

Board Station은 Mentor사의 전통적인 PCB 설계 솔루션으로 Design Manager, Design Architect, Librarian, Package, Layout, FabLink 등으로 구성되어 있다. Unix 기반에서 개발된 제품으로 X-Window를 사용하며, PC 환경에서는 MWE 에뮬레이션 환경을 통해서 사용할 수 있다.

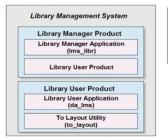

#### **LMS**

LMS (Library Management System)는 기존에 사용자 각자가 작성하여 사용하였던 라이브러리를 통합관리 함으로써 부품정보관리와 표준화, 공용화가 용이하며 각 사이트에 알맞은 부품선택 메뉴를 구성하여 사용자가 용이하게 부품을 선택하여 사용할 수 있도록 설계환경을 개선하는 시스템이다. 결론적으로 LMS는 회로입력에서 보드 설계까지의 전 프로세스를 지원하는 사내 표준화된 라이브러리를 구축, 사용하는 것을 의미하며 LMS Manager와 LMS User로 구성된다.

#### Falcon Framework

툴 통합환경을 제공하는 것으로 CUI (Common User Interface), Design Manager, AMPLE (Advanced Multi-Purpose Language) 등 이 포함되어 있다.

#### Design Manager

Design Manager는 Tool의 실행 및 Design Data의 복사, 이동, 삭제와 같은 데이터 관리 기능을 가지고 있다.

#### da\_lms

회로도 및 Logic Symbol을 작성할 때 사용되며 da\_lms는 LMS 환경에서 사용되고 Non-LMS 환경에서는 Design Architect가 사용된다.

#### Librarian

PCB 설계에 사용되는 부품의 Physical Footprint인 Geometry를 작성할 때 사용된다. 이러한 Geometry에는 Board, Component, Padstack, Via. Generic 등이 있다.

#### Package (to\_layout)

소스 회로도의 Design Viewpoint를 통하여 연결된 Net 정보 및 Design-Specific Catalog를 구성하고 Mapping 파일 등의 정보를 참조하여 PCB 데이터베이스를 구성하는데 사용된다. To\_layout은 자동 패키징 기능으로 LMS User 유틸리티이다.

#### Layout

PCB 상에서 부품의 배치 및 배선 작업을 하는데 사용된다.

#### **Board Station RE**

AutoActive 기술의 Shape-Based (Non-Grid) 방식의 Push & Shove 배선방식을 제공하는 RE는 배선 효율을 향상시킬 수 있다. Layout 툴과 상호 연동이 가능하다.

#### FabLink

Layout이 완료되었으면 PCB 제조를 위한 Gerber Data와 Drill Data, Panel Data 등을 생성하는데 사용된다. 또한, 자사 데이터 및 BOM 파 일도 생성할 수 있다.

#### Board Station XE

Board Station RE보다 더욱더 강화된 Routing 기술을 제공하며, Board Station RE와는 다르게 Layout과의 데이터 호환성을 제공하지 않는다. 멘토사의 차세대 PCB 툴인 Expedition PCB에서 사용 가능한 기능이 대부분 포팅되어 있다. Board Station XE에서 작업하기 위해서는 Board Station 데이터를 Board Station XE 데이터로 변환하는 선행작업이 필요하며, 이 작업은 자동화되어 있어서 사용자가 쉽게 데이터를 변환할 수 있다.

#### abLink XE

FabLink XE는 Board Station로 설계된 데이터는 Import 할 수 없고, Expedition PCB 또는 Board Station XE로 설계된 데이터를 Import 할 수 있다. FabLink XE를 사용하여 자동 또는 대화식 Step & Repeat Panel을 생성할 수 있으며, 이 기종의 PCB도 같이 Panel 생성이 가능하다. 또한, MOA (Manufacturing Output Automation)을 사용하여 9가(Gerber, ODB++, NC Drill, CCZ, BOM, Neutral File, Print, GDSII, IDF) 생산 데이터를 일괄 생성할 수 있다.

회사명: Mentor Graphics (Subsidiary of Ansys Inc.)

웹 주 소: http://www.mentorkr.com/ 한국지사: 한국멘토

인국시사 : 인국민도

전 화: 031) 8061-0790 주 소: 경기도 성남시 분당구 판교역로

192번길 12 (삼평동) 판교 미래에셋센터 7층

Mentor사 Board Station

18

12월 뉴스레터:레이아웃 1 14.12.15 오전 10:04 페이지 20

IDEC inside5 신진연구자

# "왜?"

## 라고 끊임없이 자신에게 묻는 연구자

정 하 연 교수 고려대학교 전자 및 정보공학과

시스템의 building block은 무조건 성능과 전력소모를 최적화하는 것보다 용도에 따라 특정 성능을 희생하고 다른 성능을 높이는 것 이 더 유리할 수 있다. 하나의 building block으로 사용될 수 있는 TDC, ADC들이 어떤 성능에 중점을 두어야 하는지를 분석하 고, 이를 통해 향상된 전체 시스템의 성능과 전력 소모를 검증에 초점을 맞춰 연구를 수행 하고 있는 고려대학교 정하연 교수를 만나보 았다.

문의 고려대학교 과학기술대학 차세대 혼성신호 회로 및 시스템 설계 연구실 전화 044-860-1429 E-mail hcchung@korea.ac.kr nics korea ac kr

## "CMOS 공정을 바탕으로 한 data link의 저전력화, 소형화, 고속화에 대한 연구"

고려대학교 세종캠퍼스 전자 및 정보공학과 정하연 교수의 전공은 혼성신호 집적회로 설계이다. 그녀는 현재, 여러 가지 애플리케이션에 사용되는 데이터 컨버터들을 어떻게 설계하는 것이 전체 시스템의 성능을 향상시키고 전력소모를 줄일 수 있는지에 대한 연구를 하고 있다

어떤 큰 틀에 작은 상자들을 빈틈없이 끼워 넣을 때 무조건 크기가 작고 반듯하게 생긴 상자 만을 골라 억지로 끼워 넣는 것보다는 틀의 모양에 따라 상자의 모습이나 크기를 결정하여 고르는 것이 더 효율적일 것이다. 그녀는 자신의 연구를 이에 비유했다. "시스템의 building block들도 무조건 성능과 전력소모를 최적화하는 것보다는 용도에 따라 때로는 특정 성능을 희생하고 다른 성능을 높이는 것이 더 유리할 수 있습니다. 제가 현재 진행하고 있는 연구는 이러한 맥락에서 하나의 building block으로 사용될 수 있는 TDC, ADC들이 어떤 성능에 중점을 두어야 하는지에 대한 분석을 하고, 이를 통해 향상된 전체 시스템의 성능과 전력 소모를 검증하는 것에 초점이 맞추어져 있습니다."

CMOS 공정을 바탕으로 한 data link의 저전력화, 소형화, 고속화란 주제로 연구하고 있다. 이는 더욱 빠르고, 가볍고, 오래가는 device를 원하는 소비자들의 변하지 않는 욕구를 충족시키기 위해 앞으로도 지속해서 연구될 분야이다. 그녀는 소비자들의 끊임없는 요구가 있는 한 계속해서 발전해 나갈 분야라며 그 중요성에 대해 이야기했다. "특히, system level에서 전체 link system의 전력소모, 성능 등을 최적화할 수 있는 각 building block들의 동작을 연구하는 데에 초점을 맞추고 있습니다. system의 각 building block들을 최적화하여 전체 성능을 높이는 데에는 한계가 있으므로 전체 system 차원에서 각 building block들의 동작을 미리 설계하여 전체 성능을 최적화하는 것이 중요하다고 생각합니다."

#### " 인생의 멘토를 만난다는 것은"

정하연 교수는 석박사 과정 중에 혼성신호 회로 중 데이터 변환기(time-to-digital converter (TDC) 및 analog-to-digital converter (ADC))와 고속 통신 인터페이스를 연구에 매진했는데, 석사 과정 중 처음으로 만든 PPL(Phase-locked loop) 칩 테스트를 하던 시기를 잊지 못한다고 한다. "처음 3일 정도 칩이 동작하지 않아 이런저런 디버깅을 하며 초조하게 보내다가 첫 신호를 발견했을 때의 그 순간이 아직도 기억납니다. 너무 기쁘고 긴장한 나머지 머리카락이 쭈뼛 서는 것 같았어요"

그녀는 지금도 자신의 아이디어를 칩으로 직접 제작하여 구체화할 수 있고, 또 그 칩이 동작하는 것을 확인하는 과정이 아직도 설레고 신이 난다고 한다. 그러면서 지금의 자리에 오기까지에는 한 분의 멘토가 있었다고 한다. "학부 과정 당시 전자회로 수업을 맡으셨던 김원찬 교수님을 기억합니다. 정년이 얼마 남지 않은 연세이셨음에도 열정적인 모습을 보며, 이분야의 매력에 대한 막연한 기대감에 교수님을 찾아뵙고 공부를 시작했습니다."

#### " "왜?" 라고 끊임없이 자신에게 묻다"

집적회로를 설계하는 사람들은 아마도 제작된 칩이 원하는 만큼의 성능을 내지 못하면 어쩌나 하는 심정 부담감을 공통으로 갖고 있을 것이다. 정하면 교수 역시, "긴시간, 큰 비용을 투자하여 만든 칩이 원하는 결과를 내지 못하면 손해가 막심하니까요. 이 부담감 때문에 테입아웃이 가까워지면 무척 예민해지기도 하는 것 같아요."라며 웃었다. 그러면서 그녀는 이를 떨쳐내는 법에 대해 이어갔다. "요즘은 설계, 시뮬레이션과 Verifiction 툴이 워낙 잘 갖춰져 있어 차근차근 모든 절차에 걸쳐 설계를 진행하면 큰 문제없이 원하는 칩 성능을 얻을 수 있는 듯해요. 그러므로 더 부지런히, 꼼꼼히 설계에 임해서 실수를 줄여 불확실성을 줄이는 것이 극복방법이 아닐까 싶어요."

또한, 그녀는 끊임없이 자신에게 질문한다고 한다. "항상 '왜? (why?)'라는 질문을 하려 노력해요. '이 연구를 왜 해야 하지?', '왜 이 공정을 사용해야 하지?', '이 소자는 왜 이렇게 그려야 하지?' 등등. '왜'가 포함된 질문은 어떤일의 방향성을 제시해 주고 전체 큰 그림에서 크게 벗어나지 않게 도와주며 새로운 아이디어를 도출함에 그 이유를 제시해 줍니다." 그녀는 연구 과제의 선정과 관련된 큰 주제로부터 트랜지스터의 크기를 가늠하는 작은 주제에 이르기까지 "왜?"라는 질문을 항상 새기는 자세로 연구에 매진한다고 한다.

#### "무어의 법칙과 어머니"

마이크로 칩에 저장할 수 있는 데이터의 양이 18개월마다 2배씩 증가한다는 무어의 법칙은 지난 60년 동안 이어져 왔다. 이는 반도체 공정을 개발하시는 분들이 이 흐름을 깨지 않으려 부단히 노력한 결과라 볼 수 있다. 현재 CMOS 공정은 그 공정의 발전이 거의 saturation 되는 시점에 있다. 이에 그녀는 "이미 이를 대체할 많은 종류의 소자들이 개발되고 있고, 머지않은 미래에 이 새로운 소자를 기반으로 한 새로운 반도체 공정이 개발되어, 무어의 법칙은 계속해서 지켜져 나가리라 믿습니다. 회로를 설계하는 사람의 입장에서는 이러한 변화에 빨리 적응하고 변화를 수용하는 것이 중요합니다."라며 미래의 변화된 반도체 산업의 적응에 대해 주목했다.

또한, 정하연 교수는 매일 연구를 하면서 전력소모를 몇 % 줄이고, 속도를 몇 % 늘리고 하는 작은 성능의 개선에 급급하다 보면, 이러한 연구가 얼마나 impact가 있는 것인지 의구심이 들 때가 있다고 한다. 하지만 작은 노력, 작은 개선 같은 작은 움직임이 모여 지속적인 반도체 산업의 육성을 이룩해 왔고, 이런 흐름은 전 세계의 사람들을 온라인상에 한데 묶어 거대한 정보 교류의 장을 마련함으로써 현재 인류가 직면한 문제들을 해결하는 데에 결정적인 역할을 할 수 있다고 말했다. "이런 의미에서 반도체 산업은 매우 뜻깊은 분야라고 생각합니다."

그리고는 그녀는 후배와 독자들에게 Intel사에서 제작한 Peter Diamandis의 "XPrize founder Peter Diamandis discusses how evolving IT enables more people to change the future" 라는 비디오를 추천했다. "이 비디오에 나와 있듯이, 향후 반도체 산업의 발전은 인류가 직면한 여러 가지 문제를 해결함에 개개인 모두의 생각을 연결시켜 더욱 효과적인 해결책을 제시하는 데에 매우 중요한역할을 할 것으로 생각해요."

두 살배기 아이의 어머니이기도 한 정하면 교수는 마지막으로 집적회로 기술을 바탕으로 소형 의료용 센서, 특히 외부 자극에 민감하고 활동량이 많은 어린이들을 위한 non-invasive 센서 시스템 개발에 대해 따뜻한 소망도 전했다. "아이들을 질병으로부터 미리 보호할 수 있는 시스템을 개발할 수 있다면 정말 의미 있는 일이 될 듯해요."

20

19

"왜?" 라고 끊임없이 자신에게 묻는 연구자