## TowerJazz 유상 MPW Service

- 목적: IDEC을 통해 지원되지 않는 공정들을 저렴하게 제작 지원

- Process: 0.18um SOI(Silicon On Insulator)/ 0.35, 0.18, 0.13um SiGe

| RF CMOS SOI Switch Technology |                            |        |              |           |           |           | SiGe Technology |                                  |                                |                     |

|-------------------------------|----------------------------|--------|--------------|-----------|-----------|-----------|-----------------|----------------------------------|--------------------------------|---------------------|

| DEVICE                        | PARAMETER                  | CA18HB | CA18QC       | C\$18Q1   | CS18Q2    | CS13Q1    | ,               |                                  |                                |                     |

| CMOS                          | VDD (V)                    | 1.8/5  | 1.8/3.3      | 2.5       | 2.5/5     | 1.2/2.5   |                 | THE RESERVE AND PERSONS NAMED IN |                                |                     |

| RFLDMOS                       | -                          | 1      | -            | -         | -         | -         | Feature         | 0.35µm                           | 0.18µm                         | 0.13µm              |

| Native NFET                   | VDD (V)                    | 5      | 3.3          | -         | -         | -         | Location        | Fab 3                            | Fab 3                          | Fab 2 and Fab 3     |

| Resistors                     | Sheet resistance (ohm/sq.) | 6, 310 | 6, 310, 1000 | 310, 1000 | 310, 1000 | 310, 1000 | CMOS FET        | Single Gate 3.3V/5.0V            | Single/Dual Gate 1.8V/3.3V     | Dual Gate 1.2V/3.3V |

| MiM<br>(Single/Stacked)       | Capacitance (fF/µm2)       | 2/4    | 2/4          | 2         | 2         | 2         | Ft Range        | 23GHz-61GHz                      | 38GHz - 240GHz                 | 37GHz - 200GHz      |

| Varactors                     | P+/nwell (fF/µm2)<br>Mos   | 1.3    | 1.3          | NA        | NA        | NA        | MIM Cap         | 1fF, 2fF and 4fF                 | 1fF, 2fF, 2.8fF, 4fF and 5.6fF | 2.8fF and 5.6fF     |

| Metal Layers                  | -                          | 6      | 4            | 4         | 4         | 4         | Poly Resistor   | 95 and 1.1K                      | 235 and 1K                     | 310 and 1K          |

| Top Metal                     | Thickness (µm)             | 2.8    | 2.8          | 2.8       | 2.8       | 2.8       | Metal Resistor  | -                                | 24                             | -                   |

|                               | Bulk                       | SOI    | SOI          | SOI       | SOI       | SOI       | Metal Levels    | 3 and 4                          | 3 to 6                         | 6                   |

- MPW Schedule

• TEL: 031-728-3114 (代) · E-mail: korea crc@cadence.com

| Process       | 1Q  |     |     | 2Q  |     |     | 3Q    |     |     | 4Q  |     |     |

|---------------|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|

|               | Jan | Feb | Mar | Apr | May | Jun | Jul   | Aug | Sep | Oct | Nov | Dec |

| SBC35         |     | 5   |     |     |     | 4   | 추후 공지 |     |     |     |     |     |

| SBC18         | 22  | 19  | 19  | 16  | 21  | 18  | 추후 공지 |     |     |     |     |     |

| SBC13         |     |     |     | 2   |     |     | 추후 공지 |     |     |     |     |     |

| CA18<br>(SOI) | 8   |     | 5   |     | 7   |     | 추후 공지 |     |     |     |     |     |

#### 연락처

TowerJazz : 하소영 과장 Office : +82-31-628-4830

IDEC : 김창수 선임 연구원 Office : +82-42-350-4424

cadence

반도체설계교육센터 사업은 산업통상자원부, 반도체산업협회, 반도체회사(삼성전자, SK하이닉스, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 세미텍, TowerJazz)의 지원으로 수행되고 있습니다.

#### 재구성형 먼티큐어 프로세서 석계 기소 동향

휴대형/내장형 매체를 통한 멀티미디어 정보 교환의 폭발적인 수요 증가로 인하여 고성능, 저전력의 시스템을 보다 작은 크기로 설계해야 하는 필요성이 어느 때보다 커지고 있다. 반면에 높은 품질의 멀티미디어 서비스에 대한 요청이 증가함에 따라 오디오 및 비디오 데이터를 처리하는 내장형 애플리케이션에 대한 기술은 고도로 발전하고 있다. 이러한 애플리케이션들은 대개 복잡한 병렬 처리 연산을 필요로 하는 특징을 지니고 있으며 일반적으로 2가지 방식 또는 그들의 조합으로 구현될 수 있다. 즉, 일반적인 내장 형 마이크로프로세서에서 실행시키는 소프트웨어 구현 방식과 주문형 반도체(Application Specific Integrated Circuit) 형태의 하드웨어 구현 방식이다. 본 고에서는 재구 성형 멀티코어 프로세서 설계 기술 동향에 대해 알아보고자 한다. (관련기사 P06~11참조)

#### 즛국 i Rin-2013 이벤트

BIT's World Congress of Industrial Biotechnology는 매년 중국에서 열리는 바이오산업 학회이다. 2013 금년 주제는 'DNA 염기서열 발견 60주년'이다. BIT Congress는 이래 세 가지 분야, 즉 '바이오 에너지, Ibio, 그리고 EB(Enzyme and Biocatalyst)'로 구성되어 있다. i-Bio 는 14개 분과로 나누어졌는데, 기술 유형별로 크게 4가지로 나눌수 있었다. 본 고에서는 이번 학회에 참석한 서울대 박영준 교수의 시선으로 i Bio-2013의 인상적인 모습들을 소개하고자 한다. (관련기사 P12~14 참조)

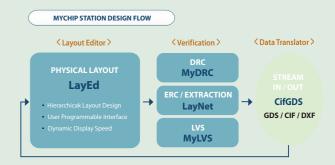

#### 덴로퀸㈜ MyChin Station Pro™

MyChip Station Pro는 국내 기술로 개발한 Layout 설계 및 검증을 할 수 있는 Design Solution 이다. Layout Editor인 LayEd Pro는 Customizable Polygon 기반으로 Mask 제작에 필요한 모든 도형을 설계할 수 있으며, Command 방식을 지원하므로 신속하고 편리하게 디자인할 수 있는 Full Custom IC Layout Editor이다. Physical Design Verification에는 Design Rule을 검사하는 MyDRC Pro와 Layout과 Schematic의 Netlist를 비교하는 MyLVS Pro로 구성되어 있으며 Parasitic information과 Netlist를 추출하는 LayNet Pro도 포함되어 있다. 본 고에서는 셀로코㈜의 MyChip Station Pro™을 소개하고자 한다. (관련기사 P16~19 참조)

# October | 2013

# MPW (Multi-Project Wafer)

| 2013년                 | 2013년 MPW 진행 현황 |                            |          |                           |          |             |            |                                                                 |           |                            |          |                          |           |                     |             |

|-----------------------|-----------------|----------------------------|----------|---------------------------|----------|-------------|------------|-----------------------------------------------------------------|-----------|----------------------------|----------|--------------------------|-----------|---------------------|-------------|

| 공정                    | MPW<br>회차       | 제작가능면적<br>(면적m²x칩수)<br>/회별 | 채택<br>팀수 | 설계면적<br>((면적)x칩수)         | DB마감     | Die<br>-out | 비고         | 공정                                                              | MPW<br>회차 | 제작가능면적<br>(면적mix칩수)<br>/회별 | 채택<br>팀수 | 설계면적<br>((면적)x칩수)        | DB마감      | Die<br>-out         | 비고          |

|                       | 119             |                            | 23       | (4x4)x23                  | 13.03.15 | 13.08.15    | PKG<br>제작중 |                                                                 | 118       |                            | 6        | (5x2 <u>.</u> 5)x6       | 13.02.27  | 13.06.12            | ★제작완료       |

| 삼성<br>65nm<br>(년3회)   | 121             | (4x4mm²)<br>× 48           | 29       | (4x4)x29                  | 13.07.05 | 13.12.06    | 제작중        | 0.35um                                                          | 120       | (5x2.5mm²)<br>× 6          | 10       | (5x2.5)x2<br>(2.5x2.5)x8 | 13.05.01  | 13.08.14            | ★제작완료       |

|                       | 126             |                            | 36       | (4x4)x36                  | 13.11.08 | 14.04.11    | 설계대기       | BCD<br>(년4회)                                                    | 123       |                            | 6        | (5x2.5)x6                | 13.08.14  | 13.11.27            | 제작중         |

|                       | 118             |                            | 23       | (4.5x4)x17<br>(4.5x2)x6   | 13,02,18 | 13.07.22    | ★제작완료      |                                                                 | 125       |                            | 7        | (5x2.5)x5<br>(2.5x2.5)x2 | 13.10.23  | 14.02.05            | 설계중         |

| MH<br>0.18um          | 120             | (4.5×4mm²)<br>× 20         | 20       | (4.5x4)x20                | 13.05.06 | 13.10.04    | 제작중        | TJ SiGe<br>(년1회)                                                | 119       | (2.5x2.5m²)<br>x 4         | 4        | (2.5x2.5)x4              | 13.03.12  | 13.07.01            | ★제작완료       |

| (년4회)                 | 122             |                            | 20       | (4.5x4)x20                | 13.07.29 | 13.12.24    | 제작중        | TJ CIS                                                          | 120       | (2.5x2.5mm²)               | 4        | (2.5x2.5)x4              | 13.05.06  | 13.09.16            | ★제작완료       |

|                       | 125             |                            | 24       | (4.5x4)x16<br>(4.5x2)x8   | 13.10.21 | 14.03.25    | 설계중        | (년2회)                                                           | 125       | x 4                        | 4        | (2.5x2.5)x4              | 13.10.14  | 14.02.17            | 설계중         |

| MH<br>0.35um          | 121             | (5×4mm²)                   | 20       | (5x4)x20                  | 13.06.17 | 13.10.04    | PKG<br>제작중 | TJ BCD                                                          | 120       | (5x2.5mm²)                 | 2        | (5x5)x1<br>(5x2.5)x1     | 13.05.20  | 13.09.16            | ★제작완료       |

| (년2회)                 | 127             | x 20                       | 20       | (5x4)x20                  | 13.12.02 | 14.03.25    | 설계중        | (년2회)                                                           | 125       | x 4                        | 2        | (5x5)x2                  | 13.10.21  | 14.02.17            | 설계중         |

| 동부<br>0.11um          | 119             | (5x2,5mm²)                 | 27       | (5x2,5)x20<br>(2,5x2,5)x7 | 13.03.20 | 13.07.31    | ★제작완료      | TJ RF                                                           | 120       | (2,5x2,5mm²)               | 4        | (2.5x2.5)x4              | 13,05,20  | 13.09.16            | ★제작완료       |

| (년2회)                 | 124             | x 24                       | 26       | (5x2.5)x20<br>(2.5x2.5)x6 | 13.09.11 | 14.01.22    | DB<br>검토중  | (년2회)                                                           | 125       | x 4                        | 4        | (2.5x2.5)x4              | 13.10.21  | 14.02.17            | 설계중         |

|                       | 120             |                            | 4        | (5x2.5)x4                 | 13.05.15 | 13.08.28    | 제작중        | * 일정은<br>* 기준 : 2                                               |           | 따라 다소 변경<br>), 26          | 형될 수     | 있습니다.                    |           |                     |             |

| 동부<br>0 <u>.</u> 18um | 121             | (5x2,5mm²)<br>x 4          | 4        | (5x2.5)x4                 | 13.06.26 | 13.10.09    | 제작중        | * 2013년 MPW 모집완료.<br>* 2014년 MPW 진행내역 및 일정은 2013년 11월에 공지될 예정임. |           |                            |          |                          |           | ļ.                  |             |

| BCD<br>(년4회)          | 123             | A 4                        | 4        | (5x2.5)x2<br>(2.5x2.5)x2  | 13.08.21 | 13.12.04    | 제작중        |                                                                 |           |                            |          |                          |           |                     |             |

|                       | 126             |                            | 5        | (5x2.5)x3<br>(2.5x2.5)x2  | 13.11.13 | 14.02.06    | 설계중        |                                                                 |           |                            | * 문      | 의 : 이의숙 (042             | 2-350-442 | 8, yslee <b>@</b> i | idec.or.kr) |

#### NDA가 체결된 Design Data 유출 금지 안내

IDEC의 MPW 참가를 통해 전달받은 Design Data 일체는 NDA를 통해서 법적인 구속력을 가지며, 관리 소홀로 인 한 외부로의 공개 또는 유출 시 개인뿐만 아니라 개인이 속해 있는 WG에 자격 박탈과 같은 강력한 규제가 가해질 수 있습니다. 협약에 의해, 형사상 책임을 물을 수 있음을 알려 드립니다. MPW 참여자 분들은 Design Data 및 관 련 자료의 관리를 철저히 하시어 불이익을 당하는 일이 없도록 거듭 당부 드립니다. NDA 체결 후 수령한 Design Kit 일체는 IDEC에 칩 수령 후 2개월 이내에 반드시 삭제하고, NDA 폐기확인서를 제출하여 제3자에 의한 공개 및 유출이 일어나지 않도록 주의 바랍니다.

#### Chip Design Contest (CDC)

- International SoC Design Conference(ISOCC) 2013 Chip Design Contest 개최

- \* Chip Design Contest(CDC)는 2013 ISOCC 프로그램의 한 세션으로 진행 되나, 제출한 논문은 프로시딩(Proceedings)에 포함되지 않음.

- 1 일정 및 장소

가, 일정 : 2013년 11월 18일(월)

나. 장소 : BEXCO Convention Hall, 부산

#### 2. 행사 진행 일정

| 구분        | 시간                 | 시간            |             |  |  |

|-----------|--------------------|---------------|-------------|--|--|

| 데모/패널 전시  | 09:00 ~ 15:00      | 09:00 ~ 15:00 |             |  |  |

|           | 세션-1 09:00         | $\sim$ 09:45  |             |  |  |

| 패널 우수팀 발표 | 세션-2 13:30 ~ 15:00 |               | - 룸 별도 배정 됨 |  |  |

|           | 세션-3 15:30         | $\sim$ 17:00  |             |  |  |

| 시상식       | 18:00 ~ 20:00      | - Banquet     |             |  |  |

|           |                    |               |             |  |  |

<sup>\*</sup> 일정은 사정에 따라 다소 변경될 수 있음.

#### 3. 시상 내역

| Award 명           | 수상팀수                                 | 내 역            |  |  |

|-------------------|--------------------------------------|----------------|--|--|

| Best Design Award | 1팀                                   | 상장 및 상금 100만원  |  |  |

| Best Demo Award   | - 3개팀           - 특별생(SSCS 서울챕터상) 1팀 | 각 상장 및 상금 50만원 |  |  |

| Best Poster Award | - 8개팀                                | 각 상장 및 상금 20만원 |  |  |

■ 제21회 한국반도체학술대회 Chip Design Contest 개최

1. 일정 및 장소

가. 일정: 2014년 2월 25일(화) 나. 장소: 한양대학교, 서울

2. 논문 마감: 2013년 10월 25일

- 논문 접수 분야 : SoC 설계

#### 3. MPW 설계팀 참여 대상

- 2013년 MPW(118회~119회, 8월말까지 제작된 공정) + 2012년 MPW 미제출팀

#### 4. 시상내역

| Award 명           | 수상팀수                                             | 내 역            |  |  |

|-------------------|--------------------------------------------------|----------------|--|--|

| Best Design Award | 1팀                                               | 상장 및 상금 100만원  |  |  |

| Best Demo Award   | <ul><li>2개팀</li><li>특별상(SSCS 서울챕터상) 1팀</li></ul> | 각 상장 및 상금 50만원 |  |  |

| Best Poster Award | - 5개팀 내외                                         | 각 상장 및 상금 20만원 |  |  |

<sup>\*</sup> 수상팀 수는 참여팀 수 등에 따라 조정될 수 있음.

#### ※ 관련 사항

\* CDC 참여와 관련한 자세한 사항은 홈페이지(http://idec.or.kr)를 참조 \* 담당: 구재희 선임(042-350-8536, kjh9@idec.or.kr)

\* 문의: 구재희(042-350-8536, kjh9@idec.or.kr)

## 「EDA Tool 소개 자료」발간 - 15개 벤더사의 62개 Tool 수록 -

IDEC EDA TOOI 소개 자료 2013년 9월

■ 구성

반도체설계교육센터(IDEC)에서 지원 하는 15개 벤더사의 62개 Tool에 대한 각각의 세부 기능과 활용법, MPW Flow 적용 가능 여부, O/S 정보등

#### © PERMANA

〈 EDA Tool 소개 자료 표지 〉

#### ■ Vendor 사 목록

| No | Vendor 명 | No | Vendor 명 |

|----|----------|----|----------|

| 1  | Actel    | 8  | Carbon   |

| 2  |          |    |          |

| 3  | Altera   | 10 | Mentor   |

| 4  |          |    |          |

| 5  | Atrenta  | 12 | Silvaco  |

| 6  | CSITEK   | 13 | Solido   |

| 7  |          |    |          |

#### ■ 배포 안내

WorkGoup(WG) 소속인 69개 대학 327명 교수들과 연구실 학생들에 게 PDF 파일로 배포

\* 문의 : 김해리(042-350-4045, hrkim@idec.or.kr)

### - 기업체 방문 강좌 운영 안내 -

저희 IDEC에서는 인재 부족을 겪고 있는 반도체 기업을 대상으로 기업에서 필요로 하는 실질적인 실무 교육을 해당 기업에 직접 방문하여 제공하는 프로그램인 "방문강좌"를 운영하고 있습니다.

홈페이지에 게재된 방문강좌 교육 목록을 참고하시어, 해당 기업에서 필요로 하는 교육을 신청해 주시면 됩니다.

기업체의 많은 관심과 신청 부탁드립니다.

#### [진행 절차]

- 교육계획: 교육 커리큘럼은 직무 수행에 필요한 내용으로 기업에서 직접 IDEC에 제시

- 강사진 구성: IDEC은 기업에서 제출한 교육 내용에 맞는 강사진을

#### ■ 기업에서 교육 공지 및 교육훈련생 확보

- 그 이 - 레드타 기어에 되자 바다라서 케디어커트에게 그 이

#### [방문 강좌 신청 방법

■ 방문 강좌 신청서 작성 후 IDEC 담당자에게 e-mail 접수

\* 문의 : KAIST IDEC 구제희 (042-350-8536, e-mail, kjh9@idec.or.kr)

## ST Discovery with ARM Cortex M4 - One Day Workshops

Seoul, Korea: 21st and 22nd October 2013

## Dear Educator & Researcher,

This October, ARM and ST Microelectronics will be running a series of one-day Microcontroller Workshops in Seoul, Korea. They will use the powerful "Discovery Board" and the "ARM MDK developmentenvironment". The venues will be Imperial Palace Seoul.

These workshops are exclusively for post-graduate members of academia, and will provide you with the knowledge needed to teach students to use these tools in Labs and Projects. Attendees who complete the full day of training will receive their own Discovery board, the MDK development environment, along with copies of all the training materials used. Our objective is simple: "train the trainer" so you are able to share this knowledge with your Students.

사전등록: http://www.e4ds.com/seminar/st\_arm\_1.asp

#### \* Seoul

Monday October 21st Start time 9:30 Tuesday October 22nd Start time 9:30

| Time          |              | Schedule                                       | ST      | ARM       |  |  |  |

|---------------|--------------|------------------------------------------------|---------|-----------|--|--|--|

| 9:30 - 10:00  | 30min        | Reception                                      |         |           |  |  |  |

| 10:00 - 10:05 | 5min         | Welcome                                        | KH Choi |           |  |  |  |

| 10:05 - 10:20 | 15min        | 5min Introductions of ST                       |         |           |  |  |  |

| 10:20 - 10:35 | 15min        | 15min Introductions of ARM                     |         | Terry Yeo |  |  |  |

| 10:35 - 10:50 | 15min        | 15min ARM Uni Pgm with ST Partnership:Overview |         |           |  |  |  |

|               | Break(10min) |                                                |         |           |  |  |  |

| 11:00 - 12:00 | 60min        | MDK-ARM Hands on Lab                           |         | Terry Yeo |  |  |  |

|               |              | Lunch(60min)                                   |         |           |  |  |  |

| 13:00 - 14:00 | 60min        | ARM Architecture & Development                 |         | Terry Yeo |  |  |  |

| 14:00 - 14:30 | 30min        | STM32 & Discovery Kit Introduction             | ST      |           |  |  |  |

|               |              | Break(15min)                                   |         |           |  |  |  |

| 14:45 - 15:15 | 30min        | ST Firmware Library Introduction               | ST      |           |  |  |  |

| 15:15 - 17:15 | 120min       | Discovery Hands on Lab                         | ST      |           |  |  |  |

| 17:15 - 17:30 | 15min        | Summary                                        |         | Tim Shi   |  |  |  |

# 재구성형 멀티코어 프로세서 설계 기술 동향

#### 숙명여자대학교 컴퓨터과학부

김윤진 교수

연구분야: VLSI/System-on-Chip 설계, 임베디드 시스템

E-mail: ykim@sookmyung.ac.kr http://esl.sookmyung.ac.kr

#### 재구성형 프로세서

요 증가로 인하여 고성능, 저전력의 시스템을 보다 작은 크기로 설 계해야 하는 필요성이 어느 때보다 커지고 있다.

반면에 높은 품질의 멀티미디어 서비스에 대한 요청이 증가함에 따 라 오디오 및 비디오 데이터를 처리하는 내장형 애플리케이션에 대 한 기술은 고도로 발전하고 있다.

이러한 애플리케이션들은 대개 복잡한 병렬 처리 연산을 필요로 하 는 특징을 지니고 있으며 일반적으로 2가지 방식 또는 그들의 조합 으로 구현될 수 있다.

즉, 일반적인 내장형 마이크로프로세서에서 실행시키는 소프트웨어 구현 방식과 주문형 반도체(Application Specific Integrated Circuit) 형태의 하드웨어 구현 방식이다.

소프트웨어 구현 방식의 경우, 다양한 애플리케이션들을 실행시킬 수 있는 장점이 있지만, 애플리케이션이 복잡해지고 커질수록 만족 스러운 성능을 낼 수 없다는 단점이 있다.

반면 하드웨어 구현 방식의 경우 소비 전력 및 성능 면에서 최적화 될 수 있으나 특정 애플리케이션에 국한된다는 단점이 있다. 이들 을 조합하더라도 소프트웨어 구현 부분은 여전히 느리고 하드웨어 구현 부분은 유연성이 결여된다.

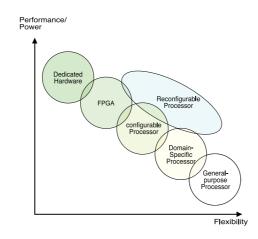

이러한 구현 방식의 한계로 인하여 내장형 마이크로프로세서와 주 문형 반도체의 중간 형태인 재구성형 프로세서를 사용하는 방식이 하나의 해결책으로 부각되고 있다. 재구성형 프로세서는 두 가지 구현 방식의 단점을 보충한다.

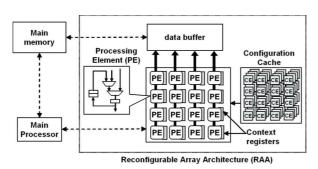

Word 단위의 data를 처리할 수 있는 PE(Processing Element) 들의 배열을 이용하여 최대한 병렬성을 살림으로써 소프트웨어 구 현 방식보다는 높은 성능을 보임과 동시에, 하드웨어 구성을 동 적으로 바꿀 수 있어서 하드웨어 구현 방식보다는 폭넓은 유연 성을 제공하기 때문에 여러 가지 애플리케이션에 쉽게 적용될

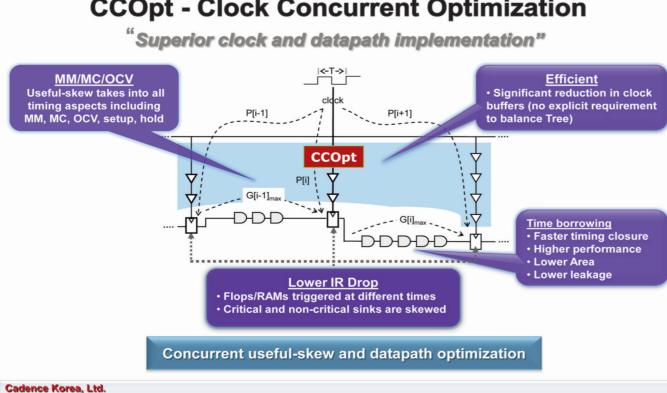

수 있다. 그림 1 (a)는 재구성형 프로세서가 차지할 것으로 기대되 휴대형/내장형 매체를 통한 멀티미디어 정보 교환의 폭발적인 수 는 위치를 보여주며, 그림 1 (b)는 일반적인 재구성형 프로세서의 구조를 나타낸다.

(a) 유연성 대비 성능/전력

(b) 일반적인 재구성형 프로세서의 구조 그림 1. 재구성형 프로세서의 예.

#### 재구성형 멀티코어 프로세서

재구성형 프로세서는 일반적인 마이크로프로세서나 하드웨어구현 방식에 비해 높은 성능과 폭넓은 유연성을 제공하지만, 하나의 재 구성형 프로세서만 사용하는 방식으로는 다음과 같은 측면에서

#### 공간적 제약성

단일 재구성형 프로세서는 애플리케이션들을 구성하는 여러 알고 리즘을 동적으로 재구성하여 데이터를 병렬 처리 할 수 있지만 이 러한 알고리즘들의 입출력으로 연결된 복잡한 미디어 스트림을 처 리할 경우 병목현상이 발생한다.

이는 전체 애플리케이션을 고려하지 않고 개별적인 알고리즘만 지 원할 수 있을 정도로 프로세서의 구성요소들 (PE Array, Configuration Memory, Data Buffer)이 공간적인 제약성을 갖고 설계되기 때문이다.

#### 설계 복잡도 증가

앞서 언급한 단일 재구성형 프로세서의 공간적인 제약성을 극복하 기 위해 크기 확대를 고려해 볼 수 있다. 하지만 이 경우 각각의 구성 요소들을 제어하는 컨트롤러들의 복잡성이 증가하면서, 프로 세서의 유연성이 떨어질 수 있다.

#### 효율적인 자원 활용 (Resource Utilization) 의 제약성

또한, 크기가 큰 단일 재구성형 프로세서의 경우 작은 애플리케이 션이 실행될 때 구성 요소들의 많은 부분이 효율적으로 사용되지 않을 수 있다. 결국, 크기 증가에 따르는 시스템 전체의 면적 비용 증가 및 높은 전력 소비는 피할 수 없는 문제이다.

#### 멀티태스킹의 제약성

단일 재구성형 프로세서에서 개별적인 알고리즘 내부의 병렬처리 는 가능하나 쓰레드/테스크 레벨의 병렬화는 구현하기 힘들다.

이러한 이유로 최근에 재구성형 프로세서 기술은 단일 재구성형 프로세서의 크기 증가를 통한 성능 개선보다는 재구성형 멀티코어 프로세서 (Reconfigurable Multi-Core Processor)를 포함한 SoC (System-on-Chip)를 이용하는 방법으로 기술이 변화하고

재구성형 멀티코어 프로세서를 포함한 SoC란 하나의 집적회로에 서 다양한 기능을 처리하는 고성능 제품 개발을 위해 여러 개의 재구성형 프로세서 및 메모리를 하나의 칩에 구현하여 다양한 알 고리즘을 구현하기 위한 시스템이다.

단일 재구성형 프로세서만 사용하는 경우 여러 개의 작업을 하나 의 PE 배열구조에서 처리했기에 크기가 크더라도 병목현상이 생 길 경우 작업 처리 속도에 제약사항이 존재한다.

그러나 재구성형 멀티코어 프로세서에서는 여러 개의 재구성형 프 로세서가 작업을 분산 처리해 효율적인 자원 활용과 멀티 태스킹 을 지원할 수 있다.

또한, 복잡한 미디어 스트림을 프로세서 간의 파이프라인 연산을 통해 단일 프로세서의 공간적 제약성 문제를 동시에 해결해주는 장점이 있다.

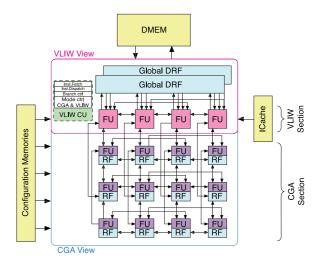

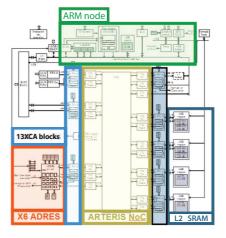

그림 2 (a)는 IMEC에서 개발된 재구성형 프로세서인 ADRES (Architecture for Dynamically Reconfigurable Embedded Systems)의 구조를 나타내며, 그림 2 (b)는 비디오 코덱을 효율 적으로 지원하기 위해 개발된 6개의 ADRES 코어들로 이뤄진 재 구성형 멀티코어 프로세서 3MF (3Multimedia multi-Format codec)의 구조를 나타낸다 [1].

(a) ADRES 재구성형 프로세서 구조

(b) 재구성형 멀티코어 프로세서 3MF 그림 2. 재구성형 멀티코어 프로세서의 예.

#### 재구성형 멀티코어 프로세서 연구 개발 동향

표 1에서 보듯이, 국외의 여러 산업체/대학에서 재구성형 프로세서 관련 연구가 수행 중이지만, 아직은 싱글코어 기반의 성능과 유연성 관련 연구 결과가 대부분이다.

하지만 최근 들어 몇몇 연구기관들에서 재구성형 멀티코어 프로세서 구조에 대한 확장 연구가 진행되고 있으며, 실제 칩 구현 사례도 발표하고 있다 (표 2).

따라서 본 단락에서는 이러한 기관들에서 수행 중인 재구성형 멀 티코어 프로세서 연구 개발 동향을 소개하고자 한다.

표 1. 국가 별 주요 연구 동향

| 국가       | 연구기관                                 | 명칭                              | 연구 범주 |      |     |  |

|----------|--------------------------------------|---------------------------------|-------|------|-----|--|

| 7/1      | 61716                                | 00                              | 싱글코어  | 멀티코어 | 저전력 |  |

| 독일       | Kaiserslautern Univ                  | KRESS Array [2]                 | 0     | ×    | ×   |  |

| 벨기에      | IMEG                                 | ADRES, 3MF, COBRA [1]           | 0     | 0    | Δ   |  |

| 네덜<br>란드 | Recore System                        | Montium 멀티코어 [3]                | 0     | 0    | Δ   |  |

|          | Stanford Univ'                       | REMARC [4]                      | 0     | ×    | ×   |  |

|          | MIT                                  | MATRIX [5]                      | 0     | ×    | X   |  |

| - I      | UC Berkeley                          | Garp [6]                        | 0     | ×    | X   |  |

| 미국       | Univ' of washington                  | RaPiDs [7]                      | 0     | ×    | ×   |  |

|          | UC Irvine                            | Morphosys,<br>Meta-Morphosys[8] | 0     | 0    | Х   |  |

|          | Carnegie Mellon<br>Univ'             | Piperench [9]                   | 0     | ×    | Х   |  |

| 일본       | Hiroshima Univ                       | I-PARS [10]                     | 0     | ×    | Х   |  |

| 영국       | 영국 Univ' of Edinburgh RICA 멀티코어 [11] |                                 | 0     | 0    | Х   |  |

표 2. 재구성형 멀티코어 프로세서 구현 사례

| 연구기관                  | 명칭                   | 코어 개수   | 공정    | 면적      | 동작속도    | 동작전압    | 전력소모량   |

|-----------------------|----------------------|---------|-------|---------|---------|---------|---------|

| UC Irvine             | Meta-<br>MorphoSys[] | 4 또는 16 | 180nm | 268mm2  | 100 MHz | 1,8 Vdd | unknown |

|                       | 3MF[]                | 6       | 90nm  | 124mm2  | 300 MHz | unknown | 700 mW  |

| IMEC                  | COBRA[]              | 2       | 40nm  | unknown | 250 MHz | 1,1 Vdd | 220 mW  |

| Recore<br>System      | Montium<br>멀티코어[]    | 4       | 130nm | unknown | 65 MHz  | 1,2 Vdd | 38,7 mW |

| Univ' of<br>Edinburgh | RICA<br>멀티코어[]       | 2~10    | 180nm | unkown  | 500 MHz | unknown | unknown |

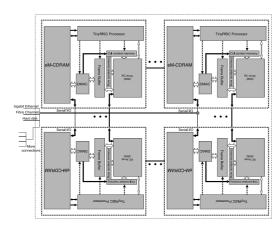

#### Meta-MorphoSys

재구성형 멀티코어 프로세서인 Meta-MorphoSys는 복잡한 병렬 처리 연산을 포함하고 있는 애플리케이션에서의 더욱 나은 성능 향상을 위해 싱글 코어 구조의 MorphoSys를 기반으로 연구개발 되 었다.

싱글 코어 MorphoSys의 경우 일반적인 마이크로프로세서나 하드웨어구현 방식에 비해 높은 성능과 폭넓은 유연성을 제공하지만, reconfigurable array를 구성하는 RC(Reconfigurable Cell)의 개수와 외부 메모리 대역폭의 제한으로 일정 수준 이상의 성능을 내기 어렵다.

이를 극복하기 위해 Meta-MorphoSys가 제안되었으며 단일 재 구성형 프로세서인 MorphoSys는 Morpho Unit이라는 명칭으로 멀티코어를 구성한다.

또한, 높은 대역폭을 지원하기 위해 embedded DRAM 타입의 eM-CDRAM (embedded Multiple-Cache DRAM)이 각각의 코어에 포함된다.

그림 3에서 보듯이 재구성형 프로세서의 공간적인 제약성을 극복하고 코어 간의 효율적인 데이터 교환을 위해 서로 다른 코어의 RC Array 사이 혹은 eM-CDRAM 사이에 연결 구조로 되어 있다.

그림 3. Meta-MorphoSys System-on-Chip 구조. 표3과 표4는 Meta-MorphoSys의 성능 향상도를 보여준다. 4개의 Morpho Unit들로 구성된 멀티코어의 경우 4배 이상의 성능향상을 보여주 며, 16개의 코어로 구성될 경우 16~18배의 성능향상을 보임을 알 수 있다.

표 3. ATR (Automatic Target Recognition) 성능 비교

| System          | 코어 개수 | 공정      | 동작속도   | 수행시간         | 성능향상도 |

|-----------------|-------|---------|--------|--------------|-------|

| MorphoSys       | 1     | 0.35 µm |        | 6ms/chunk    | 1 X   |

| Mata Manaka Ora | 4     | 0.18 μm | 100MHz | 1.33ms/chunk | 4.5 X |

| Meta-MorphoSys  | 16    | 0.1 μm  |        | 0.33ms/chunk | 18 X  |

표 4. MPEG-2 encoding 성능 비교

| System         | 코어 개수 | 공정      | 동작속도   | 수행시간    | 성능향상도  |

|----------------|-------|---------|--------|---------|--------|

| MorphoSys      | 1     | 0.35 µm |        | 104,3ms | 1 X    |

| Mata MarahaQua | 4     | 0.18 μm | 100MHz | 25.9 ms | 4.02 X |

| Meta-MorphoSys | 16    | 0.1 μm  |        | 6.33 ms | 16.5 X |

그림 4. 3MF 플랫폼 구조.

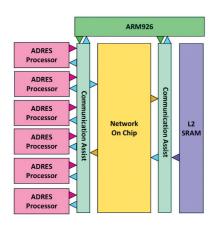

#### ADRES 계열 - 3MF

IMEC의 3MF (3Multimedia Multi-Format codec)는 ADRES (Architecture for Dynamically Reconfigurable Embedded Systems) 기반 재구성형 멀티코어 플랫폼이다 (그림 4).

ARM926 프로세서는 시스템 전체를 제어하고 6개의 ADRES 프로세서는 비디오 영상을 처리하는 프로세서이다.

ADRES 프로세서는 4x4 배열구조, VLIW 로 구성된 프로세서이 며 32-bit data-path를 제공하며 16개의 비디오 코덱을 위한 확장 명령어를 처리한다.

프로세서 코어 간 통신은 ARTERIS 의 NoC 구조를 사용하며 명령어와 데이터가 독립적으로 NoC를 통해서 통신한다.

3MF는 고용량의 데이터 처리가 필요한 셋탑박스, DVD 플레이어 및 MPEG-2, MPEG-4, H.264, VCI와 같은 다양한 멀티미디어 영상 표준을 구현하는 플랫폼으로 사용된다. 3MF의 성능은 아래와 같다.

- ► AVC/H.264 HD720p@30fps encoding

- ► MPEG4-SP HD720p@30fps encoding

- ► SVC VGA@30fps encoding

그림 5. Montium 멀티코어 프로세서.

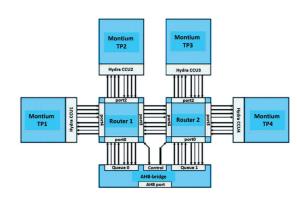

#### Montium 멀티코어

Montium 프로세서는 네덜란드의 Recore System 사에서 개발 한 재구성형 프로세서로 5개의 ALU unit들과 instruction decoding logic, sequencer logic 등으로 구성되어 있다.

개발 초기부터 DSP 애플리케이션의 성능 향상을 위한 heterogeneous multiprocessor system을 목적으로 개발되었으며, 그림 5는 최근의 Montium 멀티코어 프로세서의 구조를 보여준다.

4개의 Montium 프로세서와 CCU (Communication and Configuration Unit) 가 router를 통해 NoC 형태로 연결되어 있으며, AHB bridge를 통해 일반적인 마이크로 프로세서나 SoC의 다른 구성요소들과 통신을 할 수 있다.

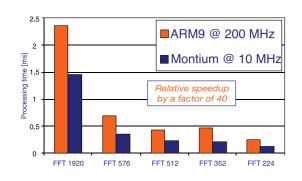

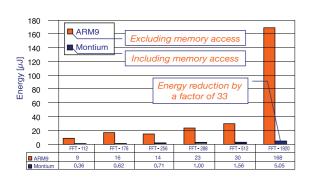

그림 6에서 보듯이 4개의 Montium으로 구성된 멀티코어 프로세서는 ARM 9 프로세서보다 40배의 성능 향상 및 33배의 에너지효율을 보여주고 있다.

(a) 성능

(b) 에너지 소모량 그림 6. 성능/에너지 소모량 비교 (ARM9 프로세서 - Montium 멀티코어 프로세서).

#### RICA 멀티코어

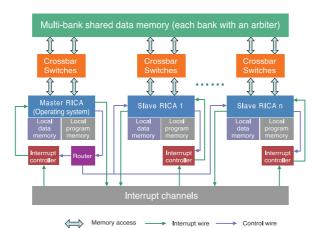

RICA (Reconfigurable Instruction CELL Array)는 영국의 Univ. of Edinburgh에서 연구 개발된 재구성형 프로세서로 여러 종류의 산술/논리 연산을 지원하는 8x8 instruction cell array, multi-bank data memory, program memory 등으로 구성되어 있다.

초기에는 domain-specific reconfigurable array라는 타이틀로 개별적인 DSP 알고리즘에 특화된 재구성형 프로세서에 관한 연구가 대부분이었으나 광대역 무선접속 표준의 하나인 WIMAX (Worldwide Interoperability for Microwave Access)를 고성

능으로 구현하기 위해 재구성형 멀티코어 프로세서에 관한 연구로 확장되었다.

RICA 멀티코어 프로세서의 구조는 그림 7과 같다. 각각의 RICA 프로세서는 shared memory에 접근할 수 있으며 자신만의 interrupt controller를 가지고 있다.

하지만 오직 하나의 코어 (master core)에서만 task 관리를 위한 운영체제가 실행되며 나머지 코어들은 slave로 작동한다.

이러한 master—slave 멀티코어 구조로 소프트웨어를 단순화 하 였으며, Single Program Multiple Data (SPMD) 방식으로 성 능을 향상시킨다. 표 5 는 RICA 멀티코어 프로세서의 성능 향상도 를 보여준다.

2개의 RICA 프로세서들로 구성된 멀티코어의 경우 2.12배/1.42 배 (Transmitter/Receiver)의 성능향상을 보여주며, 10개의 코 어로 구성될 경우 7.28배/12배 (Transmitter/Receiver)의 성능 향상을 보임을 알 수 있다.

표 5. WIMAX 성능 비교

| System    | 코어 개수 | Transmitter<br>(Throughput) | Receiver<br>(Throughput) | 성능향상도       |          |

|-----------|-------|-----------------------------|--------------------------|-------------|----------|

|           |       |                             |                          | Transmitter | Receiver |

| RICA      | 1     | 445 kbps                    | 55 kbps                  | 1 X         | 1 X      |

| RICA 멀티코어 | 2     | 942 kbps                    | 78 kbps                  | 2,12 X      | 1.42 X   |

|           | 10    | 3,241 kbps                  | 659 kbps                 | 7.28 X      | 12 X     |

그림 7. RICA 멀티코어 구조.

#### 맺음말

최근 다양한 멀티미디어와 유무선 통신 시스템이 디지털화 및 고 성능화되면서 시스템 사양이 점점 거대하고 복잡해지며 SoC(System-on-Chip) 시장에서는 더 높은 성능의 다양한 제품이 요구되고 있다.

또한, 멀티미디어 애플리케이션들의 표준도 빠르게 변하고 있어서 이들은 점점 더 복잡한 알고리즘을 사용하면서 다양하게 발전하고 있다

이러한 변화 및 복잡도를 갖는 애플리케이션들을 휴대형/내장형 매체에서 구현하기 위해서는 고성능 및 유연성을 모두 갖추고 있 는 시스템 설계 기술이 필요하다.

이러한 요구를 만족시킬 수 있는 한 가지 방법이 재구성형 멀티코 어 프로세서를 사용하는 것이다. 재구성형 멀티코어 프로세서는 단일 재구성형 프로세서가 지닌 고유의 병렬성을 확장하여 성능을 극대화하고, 동시에 재구성을 통하여 비용과 복잡도를 완화하고 유연성을 추구한다.

그러므로 앞으로 이러한 고성능 및 유연성을 모두 갖춘 재구성형 멀티코 어 프로세서의 설계 기술은 핵심 기술로 대두할 것으로 전망한다.

## Reference

[1] http://www2.imec.be

[2] Reiner Hartenstein, M. Herz, T. Hoffmann, and U. Nageldinger, "KressArray Xplorer: a new CAD environment to optimize reconfigurable datapath array architectures," in Proc. of Asia and South Pacific Design Automation Conf., pp. 163–168, January 2000.

[3] http://www.recoresystems.com

[4] T. Miyamori and K. Olukotun, "A quantitative analysis of reconfigurable coprocessors for multimedia applications," in Proc. of IEEE Symoposium on FPGAs for Custom Computing Machines, pp. 15–17 April 1998

[5] E. Mirsky and A. DeHon, "MATRIX: a reconfigurable computing architecture with configurable instruction distribution and deployable resources," in Proc. of IEEE Symposium on FPGAs for Custom Computing Machines, pp. 157–166, April 1996.

[6] John Reid Hauser, "Augmenting a Microprocessor with Reconfigurable Hardware," Ph.D. Dissertation in UC Berkeley, 2000.

[7] Darren C, Cronquist, Chris Fisher, Miguel Figueroa, Paul Franklin and Carl Ebeling, "Architecture Design of Reconfigurable Pipelined Datapaths," in Proc. of the 20th Anniversary Conf. on Advanced Research in VLSI, pp. 23–40, March 1999.

[8] Guangming Lu, "Modeling, Implementation and Scalability of the MorphoSys," Ph,D, Dissertation in UC Irvine, 2000,

[9] S. C. Goldstein, H. Schmit, M. Budiu, S. Cadambi, M. Moe, R. Taylor, "PipeRench: A Reconfigurable Architecture and Compiler", IEEE Trans. on Computer, Vol. 33, No. 4, pp. 70–77, April 2000.

[10] K. Tanigawa, T. Kawasaki and T. Hironaka, "A coarse-grained reconfigurable architecture with low cost configuration data compression mechanism," in Proc. of International Conference on Field-Programmable Technology, pp. 311–314, December 2003,

[11] W. Han, Y. Yi, M. Muir, I. Nousias, T. Arslan and A.T. Erdogan, "Multicore Architectures with Dynamically Reconfigurable Array Processors for Wireless Broadband Technologies," IEEE Trans. on Computer Aided Design, Vol. 28, No. 12, pp. 1830–1843, December 2009.

IDEC | 기획칼럼 I

중국은 새로운 기술과 산업의 탄생을 위해 서 목하 진통 중이다. 거대한 땅, 인구가 신 천지를 향해서 돌진한다. 각 분야에서 중국 을 본 사람들은 최첨단부터(최근 유인우주 선 실험에 성공했다.) 짝퉁에 이르기까지 다양성에 놀란다. 그중 한 분야가 바이오산 업이다.

중국의 힘은 거대한 인력 풀이다. 특히 지 난 세기 노예성 이민을 시작으로 한 중국인 들이 뿌리가 세계 도처에 뿌리내렸다. 특히 미국 서부 철도 노동자로 시작된 중국의 이 민 3세들이 이제 실리콘 밸리의 중추를 이 루고 있다. 이들이 지금은 중국으로 금의환 향하고 있다.

# 중국 i Bio-2013 이벤트

중국이 주최하는 바이오산업학회

중국은 새로운 기술과 산업의 탄생을 위해서 목하 진통 중이다. 거대한 땅, 인구가 신천지를 향해서 돌진한다. 각 분야에서 중국을 본 사람들은 최첨 단부터(최근 유인우주선 실험에 성공했다.) 짝퉁에 이르기까지 다양성에 놀란다. 그중 한 분야가 바이오산업이다.

중국의 힘은 거대한 인력 풀이다. 특히 지난 세기 노예성 이민을 시작으로 한 중국인들이 뿌리가 세계 도처에 뿌리내렸다. 특히 미국 서부 철도 노동 자로 시작된 중국의 이민 3세들이 이제 실리콘 밸리의 중추를 이루고 있다. 이들이 지금은 중국으로 금의환향하고 있다.

이들이 이루려고 하는 일이 첨단 바이오산업이다. 바이오산업을 통해서 식량 문제를 해결하고, 에너지 문제를 해결하고 질병을 퇴치하고자 하는 것이다. 중심에 i Bio라는 학회가 서 있다. 이 학회는 DNA 구조가 밝혀진지 60주년이 되는 해인 2013년을 기념해서 열렸다. DNA 구조가 발견된 것은 트랜지스터가 발명된 것보다 5년 늦은 일이다. 반도체 기술은 무어의 법칙에 따라서 발전해서, 이제 칩 하나에 지구인구 숫자와 맛 먹은 트랜지스터를 집적하게 되었다. 아래 그림과 같이 1965년도에는 만화에서나 상상할 수 있었던 1,000불 컴퓨터를 개인이 하나 이상 가지게 되었다. 마찬가지로 그동안 DNA를 중심으로 한 분자 생물학 역시 비약적으로 발전하였다. 이제 인간 게놈 분석을 1,000불에 하는 이야기는 만화 속의 상상이

아니다. 10년 이내에 첫 돌 선물로 DNA 정보를 가진 메모리를 선물하게 될 것이다.

이러한 시기에 중국은 분자 생물학을 중심으로 13억 인구가 해결해야 할 에너지, 식량, 그리고 환경 문제를 바이오 기술로 풀어보고자 하는 것이다.

-BIT's World Congress of Industrial Biotechnology는 매년 중국에서 열리는 바이오산업 학회이다. 2013 금년 주제는 'DNA 염기서열 발견 60주년'이다. BIT Congress는 아래 세 가지 분야, 즉 '바이오 에너지, Ibio, 그리고 EB(Enzyme and Biocatalyst)'로 구성되어 있다.

개막식에서는 4명의 노벨 수상자를 초청하여 다음과 같은 네 가지 발견과 이 발견이 현대 바이오 기술에서 가지는 의미에 대해서 듣는 자리이다. 만 명에 가까운 참여자들이 자리를 뜨지 않고 바이오 학자들의 발견스토리와 이후 발전 스토리를 경청하였다.

- 1) Richard J. Roberts의 Bacterial Methylomes

- 2) Avram Hershko의 Ubiquitin-mediated protein degradation 이 건강과 질병에 미치는 영향

- 3)Rolf Zinkernagel의 Non retroviral RNA virus integration into Host RNA

4) Ferid Murad의 Discovery of Nitric oxide와 Cyclic GMP의 역할 5) Erwin Neher의 Ion channel의 발견이다.

공통된 특징은 이들 노벨 수상자들 중 대부분이 고령자임에도 현재에도 연구와 자문에 참여하고 있다는 사실이다. 그리고 발표 중 느껴지는 연구에 대한 열정이 놀라웠다.

#### -난징

난징은 중국 삼국시대 오나라 시대의 수도였으며, 남경대학살의 슬픈 역사를 가지고 있다. 그리고 장강이라고 불리는 '양쯔강'의 하류에 자리 잡고 있다. 어부가 고기를 잡던 옛 서정은 없어졌다. 이제 거대한 하구의 개발이 있을 뿐이다. 새벽 잠시 들른 장강 하류는 옛 정취의 끝자락을 잠시 보여줄 뿐이다. 양자강 끝자락에서 다시 학회로 돌아오는 아침 8시 난징의길은 그야말로 자동차와 자전거 물결이다. 새벽 양쯔강 방문은 15분, 돌아올 때는 1시간이 넘게 걸렸다.

#### 바이오산업의 새로운 동향

i-Bio 는 14개 분과로 나누어졌는데, 기술 유형별로 크게 4가지로 나눌 수 있었다.

- -식품: Functional food, Natural products, Agricultural and Plant -재료, 의료재료: Novel bio materials, Biodegradable polymers and plastics, Tissue engineering

- -환경 및 에너지; Food quality and safety, Environmental biotechnology

- -바이오 플래트 폼; 합성 생물학(Synthetic biology), Microorganism technology

Fermentation and metabolic engineering, Biomedical and instrumentation 필자가 IT 전문가의 입장에서 느낀 몇 가지 인상을 소개한다.

#### 중국의 농부에게

가장 인상적인 발표는 네덜란드에 본사를 둔 DSM의 미국지사인 DSM biobased products & Services의 Hartig씨1)의 발표였는데, 첫째는 기술이 인상적이다. 바이오 스탁(사탕수수 등 바이오 셀루로즈 등)을 이용하여 바이오 에탄올을 만드는 공정이 현재 석유기반보다 가격이 70%이면서도 성능이 비슷한 수준을 달성하였다. 이 회사는 POET사와 합작해서 미국에서 년 2,000만 배럴 이상의 셀룰로스 에탄올을 생산하는 LIBERTY프로젝트를 시작했다.

둘째는 좀 더 거시적인 관점이다. 즉, 중국이나 제삼 세계에서도 대단위로 일어나고 있는 도시화에 대한 것이다. 도시화가 가지는 환경 문제를 이러한 새로운 인프라로 해결할 수 있다는 것이다. 즉, 농부가 단지 부가가치가 낮은 농산물을 생산하는 것에서 벗어나, 새로운 첨단 산업 즉 셀룰로스를 기반으로 하는 바이오 에너지생산에 이바지하게 함으로써, 소득뿐만이 아니라 자긍심을 심어줄 수 있다는 것이다. 즉 농업이 미래 지속 가능한산업이며 중요한 첨단 산업의 일부라는 점을 부각하는 것이 중요하다는 것이다. 남한의 도시화뿐만이 아니라, 북한의 산업화를 일부나마 책임질 미래를 가지고 있는 우리에게 많은 시사점을 주고 있다.

#### 거대한 흐름; DNA 분석 그리고 합성 생물학 그리고 통제

역시 바이오 기술의 꽃은 DNA 분석의 신속화, 저렴화 그리고 이에 기반을 둔 합성 생물학의 발전이다. 재료 및 에너지 분야에서 가장 중요한 것은 석유제품과 경쟁할 수 있는 공정을 개발하는 것이다. 진화가 만들어 낸생물 프로세스, 즉 물질을 제조 공정에서 공정률을 제어하는 부분(rating limiting process, 주로 단백질, 그리고 O2 등 가스)을 이해하고 이를 필요시 가속시키는 효소물질의 개발하고 적용하는 분야다.

이러한 합성 생물학을 가능하게 하는 기술의 진보는 IT 기술, 특히 정보처리 기술(Bio informatics)과 나노, 멤즈기술과의 융합이다. NGM(Next generation Genome sequencing)이 유전자 분석을 1,000불대에 가능 하게 했다면, 새로운 유전자 합성 기술은 박테리아, 효모, 그리고 바이러스 를 조작해서 새로운 물질, 에너지, 그리고 안전을 담보할 수 있는 새로운 바이오 기술의 플래트 폼을 제공할 것이다.

#### IT와 융합된 환경제어기술

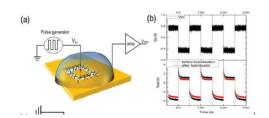

IT와 연계된 주목할 발표는 LED를 이용한 환경 감시 센서 시스템의 구축이다. 이 부분의 발표는 호주의 뉴캐슬 대학의 싱가포르 분교연구소의 연구자가 발표했다. 최근 중요한 환경 모니터링 수요 중의 하나가, 물, 특히 강물의 실시간(real time monitoring)이다. 즉 필요 시 수질 검사를 분석실에서 하는 대신, 실시간으로 모니터링하는 요구가 늘어나고 있다. 식수가 오염되었을 때, 이를 즉시 경고하는 것이 중요하기 때문이다. 여름철오염원에 의해서 녹조류 등에 의한 독성의 오염을 즉시 경고하기 위해서 LED를 사용하는 아이디어와 실제 모니터링 결과를 발표하였다. 370nm-710nm 파장의 7개 LED 조합을 물에 쪼여서, 이들 각각에 의한 '형광 응답'을 측정함으로써, 클로로필-a와 녹조류(혹은 cyanobacteria)의 농도를 유추할 수 있는 시스템이다.

#### 새로운 재료와 식량

생물의 세포와 세포 내부에서 일어나는 생명현상은 자연계가 만들어낸 가장 놀라운 메커니즘이다. 이 메커니즘에는 정보과학, 열역학, 그리고 유기물질과 무기물질의 인터페이스가 들어있다.

산업혁명 이후, 인류가 대량의 에너지와 부기물, 유기물을 사용하여 구조물, 기능재료를 만들어 내었다면 미래의 재료는 자연의 고에너지 효율, 그리고 유기/무기 다양성을 흉내 낸 재료에서 부가가치를 찾는 시대가 될 것이다.

첫째는 의료에의 응용이다. 바이오 기술을 이용한 피부, 장기의 제조, 그리고 줄기세포의 저렴한 공급이 중요한 테마이다.

둘째는 지속적인 식품 공급의 안전성을 보장하기 위해서 농토(장)의 생산성 향상이 중요하다. 해충, 토양의 소실, 그리고 기후 변화, 그리고 외부 농식물의 침투 등의 도전을 예측하고 이를 최소화함으로써 지속적인 생산을 보장해 주는 기술이 필요하다. 그 외에도 바이오 degradable 플라스틱, 환경 무해 재료 물질의 탐구가 지속하고 있다.

#### IT와 결합하는 바이오 센서의 새로운 가능성

이번 학회에서 느꼈던 것은 바이오 기술과 IT가 충분히 융합되고 있지 않다는 점이다. 특히 IT와 결합한 바이오 센서에 대한 연구, 이를 이용 한 바이오 생산성의 향상에 대한 폭넓은 연구가 아직 주목을 받고 있지 못하다는 느낌을 받았다.

가장 큰 이유로는 믿을 만한 IT 센서 기술의 부재를 들 수 있다. 생물은 가장 자연이 만들어 낸 가장 진화된 '나노 바이오 센서'라고 할 수 있다. 생물이 스스로 '아이덴티티'를 유지하고 다음 자손에게 전 세대에서 받은 'DNA'와 자기가 획득한 형질(경향성)을 물려주기 위해서 발전된 '인지기능'은 척박한 환경(특히 물, 화학적 환경)에서 진화한 것이다. 피부의 촉각기능, 혀의 미각 기능, 눈의 시각 기능 등 현대 나노 재료, IT 기술로 이를 흉내 내기조차 힘들다. 특히 한번 센싱 후, 회복하는 생물의 센서 기능은 가히 기적에 가깝다.

따라서 IT 기술이 바이오산업에 광범위하게 사용되기 위해서는 '자연이 진화시킨' 바이오 센서 정도의 기능이 필수적이라는 사실을 알 수 있다. 인간이 따라가지 못하는 바이오 센서 부분은 결국 세포가 가지고 있는 '바

#### IDEC I 기획칼럼 I

이오 안테나'이다. 생물은 주로 세포의 벽에 '분자 안테나'를 두고 분자 안테나에 센싱하고자 하는 분자, 바이러스, 박테리아와 결합하도록 한다. 이러한 마치 무선 안테나가 공기 중의 수많은 전자파 중에서 원하는 주파 수 대역을 필터링하는 것과 같다.

#### 높은 선택성의 부재

전자파 안테나는 공기 중에서 존재하는 특정 주파수의 작은 크기의 신호를 잡아낸다. 원리는 높은 Q 팩터(공명 주파수)를 유지하는 회로, 재료 기술 이다. 세포는 세포막 단백질과 세포 내의 (주로) G 단백질의 높은 분자 Q 팩터에 의해서 피 속의 분자 유무를 알아낸다. 약간의 차이는 있지만, 눈, 코, 피부, 혀, 눈 등 감각기관은 이러한 원리에 기초한다.

인간이 만든 바이오 센서는 이러한 Q 팩터를 유지하지 못한다. 그리고 다 시 사용하는데 필요한 씻기(relaxation) 메커니즘을 가지지 못하고 있다. 즉, 가장 필요한 기술은 생물 센서 수준의 재료, 그리고 용액과의 인터페 이스 기술이라 할 수 있다.

#### 신호처리는 용이

일단 높은 선택성, 그리고 신뢰성 있는 릴랙세이션(씻기) 프로세스를 가지 면 이후 신호처리는 비교적 용이하다. 마치 CIS(CMOS 시각 Image sensor) 센서가 채용하고 있는 잡음 제거 기술 등을 채용해서 신호처리와 이를 디지털 정보화, 통신 시스템과의 연결은 비교적 용이하다.

필자가 i-Bio 2013에서 발표한 반도체 기반 C chp 기술은 생물 분자센 서 수준의 물질이 개발되기 전, 현재의 반도체 칩 기술, 그리고 나노기술 (CNT 기반)을 융합하고 신호 처리 기술을 극대화하기 위한 노력을 보이고 있다. 센서는 아래 그림과 같이, 금 나노 입자를 장착한 CNT 채널을 가지 는 센서 셀과 금 나노에 공유결합으로 장착된 프로브 물질, 그리고 이를 약 4,000개 정도 장착하고 있는 반도체 칩으로 구성되어 있다. 감도는 금 나노입자와 CNT의 전기적 접합이 금 나노입자에 장착된 프로브 물질과 타겟 물질의 결합으로 그리고 선택성은 전극에 가해지는 여러 가지 전기 신호에 의해서 얻어진다. 금 나노 입자에 장착된 프로브 물질을 변화시킴 으로써, DNA뿐만이 아니라, 단백질 센서로도 확장할 수 있는 플래트 폼이다.

그림, 저자가 발표한 반도체 바이오 센서 플래트 폼인 C chip. 각각 1k 4k 센서 셀을 장착하고 있다. 한 개 셀은 금 나노 입자가 장착된 CNT를 채널로 가지고 있다. 그리고 금 입자에 프로브 물질을 붙여 필요한 타겟 분자를 측정한다. 다양한 전기 신호를 가함으로써. 선택성과 감도를 얻을 수 있다.

중국 난징에서 개최된 ii Bio(Industrial Bio)의 참가를 계기로 IT 공학자 의 측면에서 본 바이오산업의 현황을 소개하였다.

핵심은 세 가지로 요약할 수 있다. 첫째, 중국은 막강한 우수 인력, 그리고 정부 주도 자본력을 바탕으로 바이오산업에 투자하고 있고. 서구의 기술. 자본이 들어오고 있다

둘째, 바이오산업은 농부, 농업에 새로운 비전을 불어넣음으로써, 맹목적인 도시화를 저지할 수 있는 동력을 제공할 수 있다.

셋째, 바이오산업은 아직 IT와 적극적으로 융합되고 있지 못하며, 가장 큰 이유는 신뢰성 있는 센서의 부재이다.

본 컬럼이 IT 강국인 한국이 거대한 중국이라는 바이오 관련 시장을 곁에 두고 새로운 가능성을 찾는데 도움이 되기를 바란다.

#### 참고 문헌

- 1) S. Hartig, Cellulosic ethanol; a commercial reality in the USA! What is next? Brazil or China? i-bio, Nanjing, 2013

- 2) C.C.Lee, Harnessing bioluminescence and Fluorescence technologies for rapid real time monitoring of water quality. i-bio, Nanjing, 2013

- 3) P. Miller, Satisfying food demand through technologies, i-bio, Nanjing, 2013

- 4) Y.J.Park, C chip; applications to electrical DNA sensing and immuno assav. i-bio. Naniing . 2013

서울대학교 전기정보공학부 / SK하이닉스 석좌교수

연구분야: 반도체 소자 물리. 분자 FET E-mail: ypark@snu.ac.kr http://semiplaza.snu.ac.kr

#### IDEC Newsletter • 14 | 15

### **ISOCC 2013**

Sunday-Tuesday, November 17-19, 2013 **BEXCO Convention Hall, Busan, Korea**

http://www.isocc.org (Main Theme: SoC Design for Creative Future Technology)

## **2013 International SoC Design Conference Call for Papers**

#### premier SoC design forum for leading researchers from academia and industries. Prospective authors are invited to submit papers of their original works emphasizing contributions beyond the present state of the art. ISOCC 2013 is technically co-sponsored by IEEE CAS Society and accepted papers will be published on IEEE Xplore. We also welcome proposals on special sessions.

International SoC Design Conference (ISOCC) aims at providing the world's

Complete 2-page to 4-page manuscript (in Standard IEEE double-column format) is requested. Papers must be submitted electronically in PDF format. Only electronic submission will be accepted. For more information, please refer to the conference website: http://www.isocc.org.

#### **Areas of Interest**

Analog and Mixed-Signal Circuits Display Driver and Imaging Devices Embedded System Software Low Power Design Techniques Energy-Aware Systems Multimedia (A/V) SoCs Wireline & Wireless Ics (RF ICs) SoC Testing and Verification

Communication SoCs Embedded Memories High Speed Signal Interfaces Microprocessor and DSP Architectures SoC Design Methodology SoCs for Automotive Technology Sensor & MEMS Signal Integrity/Interconnect Modeling Power Electronics (Energy Harvesting) Bio & Medical devices

#### **Special Sessions**

Proposals are solicited for special sessions. Please submit proposals for special sessions to the special session chair.

#### **Chip Design Contest**

Design contest provides the academia with the opportunity to introduce their novel chip designs to the real world. The selected designs will be awarded.

#### **Best Paper Awards**

The authors of selected papers will be awarded for technical contributions and their papers will be invited for publication in the Journal of Semiconductor Technology and Science (SCIE) published by Institute of Electronic Engineers of Korea (IEEK). (Visit www.jsts.org for submission details).

#### **Important Dates**

| <ul> <li>Deadline for submission of special session proposal;</li> </ul>   | 01 Jul. 2013 |

|----------------------------------------------------------------------------|--------------|

| <ul> <li>Acceptance notice of special session proposal;</li> </ul>         | 01 Jul. 2013 |

| <ul> <li>Deadline for submission of regular session full paper;</li> </ul> | 21 Jul. 2013 |

| <ul> <li>Deadline for submission of chip design contest;</li> </ul>        | 21 Jul. 2013 |

| <ul> <li>Deadline for submission of special session full paper;</li> </ul> | 21 Jul. 2013 |

| <ul> <li>Notification of acceptance (all submitted papers):</li> </ul>     | 01 Sep. 2013 |

| <ul> <li>Deadline for author and early-bird registration;</li> </ul>       | 15 Sep. 2013 |

At least one author of each accepted paper must register by September 15, 2013.

UDEC | 기획칼럼 Ⅱ

# 셀로코㈜ MyChip Station Pro™

#### 고전

Full custom Layout & Verification

#### 개요

MyChip Station Pro는 국내 기술로 개발한 Layout 설계 및 검증을 할수 있는 Design Solution 입니다. Layout Editor인 LayEd Pro는 Customizable Polygon 기반으로 Mask 제작에 필요한 모든 도형을 설계할 수있으며 Command 방식을 지원하므로 신속하고 편리하게 디자인할 수 있는 Full Custom IC Layout Editor입니다.

Physical Design Verification에는 Design Rule을 검사하는 MyDRC Pro와 Layout과 Schematic의 Netlist를 비교하는 MyLVS Pro로 구성되어 있으며 Parasitic information과 Netlist를 추출하는 LayNet Pro도 포함되어 있습니다. 이러한 Verification Tool은 사용자가 정의한 룰 파일을 사용할 수 있으며 DRACULA™와 호환도 가능합니다.

CifGDS Pro는 설계된 Layout Data를 Industry Standard format(GDSII,CIF, DXF, Ansys)으로 import/export할 수 있으며 상호 변환(Translator)도 가능합니다.

MyChip Station Pro는 Windows 환경에서 운영되어 초보자들이나 학교에서도 쉽게 배울 수 있으며 사용하기 편리할 뿐 아니라 저렴한 가격으로 제공되고 있습니다. 또한 기존의 IC 설계 분야를 기반으로 MEMS, MASK, FPD(LCD/LED/OLED) 등의 분야에서 사용되는 도형들을 간편하게 Editing 할 수 있도록 여러 기능들을 추가,개선하였으며 VBS(Visual Basic Script)를 이용하여 단순/반복적이거나 복잡한 도형들을 쉽고, 간편하고, 빠르게디자인할 수 있는 기능을 지원하고 있습니다.

현재 국내의 수많은 대학교 반도체/나노, 전기/전자, 기계/메카트로닉스, MEMS 관련학과에서 MyChip Station를 활용하여 설계 교육을 진행하고 있으며, 산업체에서는 IC Layout, MEMS Design, LCD/OLED, Optical, MASK 및 관련 분야의 Layout 설계에 사용하고 있습니다.

또한, 미국, 일본, 유럽, 중국, 인도 등에서 설계 전문회사의 전문가들로부터 Analog 및 Mixed IC 설계에 수년간 사용되며 뛰어난 성능을 입증받고 있습니다.

#### Supported platform and O/S System

- Window 98, NT

- Window XP, 7(Vista), 8

#### 구성

#### MyChip Station Pro™

- LayEd Pro : A Full Custom Layout Editor

- CIF/GDS Pro: CIF/GDSII Translator

- MyDRC Pro: A Design Rule Checker

- LayNet Pro : SPICE Netlist Extractor & Electrical Rule Checker

- MyLVS Pro: Layout & Schematic Netlist Comparator

#### 특성 및 기능

#### 특징

- 순수국내기술로 개발

- 1990년 국내 최초로 개발, 국내 유일의 EDA Tool

- Windows 환경에서 운영

- 타 프로그램의 경우 UNIX, LINUX 환경에서 운영

- 사용의 편리성, 접근성 용이

- 초보자들이나 학교에서도 쉽게 배우고 사용

- 포토마스크제작 전용 프로그램

- 일반CAD는 Layer 가 물질구성이 아니라 단순색상을 표현

- 최종 결과 포맷의 차이 (표준포맷 : GDSII)

- MEMS, FPD 등의 설계지원

- 다양한 Editing기능으로 어떠한 도형도 설계 가능

- VBS (Visual Basic Script) 사용으로 복잡하고 대량의 도형 설계가능

- 다양한 포맷(GDSII, DXF, CIF)을 지원

- AutoCAD의 DXF 호환가능 (DWG 추가예정)

- Cadence, Synopsys 등의 GDSII 호환 가능

- DXF. GDSII 간의 상호 호환가능

#### Layout Editor (LayEd Pro)

Hierarchical layout design : Hierarchy 구조의 설계 가능 Edit-in-place를 사용하여 편집 가능

Command line interface: 마우스 외에 명령어로도 모든 메뉴 사용 가능 Command Helper를 통한 command 설명 및 예제 지원

Journaling & Backup Project

갑작스러운 시스템 다운 시에도 Journaling 기능으로 마지막 데이터 복구 및 Backup Project 기능을 통해 설계 자료를 백업할 수 있다.

#### Macro

여러 가지 명령어를 하나의 명령어로 만들어 실행

셀로코㈜ MyChip Station Pro™

Customizable bind keys

Bind key와 Toolbar를 사용자가 원하는 메뉴로 만들어 사용

User Programmable Interface

VBS(Visual Basic Script)을 사용 가능하여 복잡하고 대량의 디자인을 간단히 설계할 수 있음

#### Powerful editing

Rotate/Reflect/Array objects, Edit edge or vertex / Stretch objects / Edit edge or vertex

#### Auto Wiring

수평, 수직 방향으로 wire를 손쉽게 생성할 수 있다

Make Cell from Selected Objects

선택한 오브젝트를 바로 Cell로 만들 수 있으며 추가로 바로 생성된 오브 젝트의 인스턴스로 치환할 수 있다.

#### Enhanced Selection

마우스 드래그 방향에 따라 오브젝트 선택 정책을 다르게 할 수 있으며 또한 새로 추가된 다이얼로그 인터페이스를 통해 다양한 옵션으로 오브젝트를 선택 및 비 선택을 택할 수 있다.

#### Enhanced Snap

Intersection point에도 스냅이 적용되며 Ruler 사용 시 snap 적용 여부 = 선택할 수 있다.

#### Enhanced Sizing

Size 기능에 원하는 area를 지정해서 선택한 오브젝트를 확대 및 축소 시킬 수 있다.

Enhanced Create Bitmap 원하는 영역만 지정해서 화면 캡쳐 할 수 있는 기능

Cross Section View Layout 단면도(Cross Section View) 지원

Mentor Calibre Error display

Mentor Calibre에서 나온 에러 결과를 볼 수 있는 기능

Message for Calibre DRC rule

ANSYS format support

3D MEMS 해석을 위해 Ansys 인터페이스 포맷 지원

#### Verification (MyDRC Pro, LayNet Pro, MyLVS Pro)

MyChip Station - Verification Tool은 MyDRC, LayNet, MyLVS 세 가지로 분류되어 있으며 각 Tool은 순차적으로 사용자가 설계한 Layout을 검증하게 된다. MyDRC는 사용자가 설계한 Layout이 특정 공정의 Design rule 또는 사용자가 직접 정의한 rule에 의해 적합하게 설계되었는지 검증을 해주며 LayNet은 Layout의 Netlist를 추출하는 기능을 가지고 있다.

마지막으로 MyLVS는 Layout에서 추출한 Netlist를 MyAnalog에서 추출한 Schematic Netlist와 비교를 해서 Layout이 Schematic과 동일하게 설계되었는지를 검증하는 기능을 가지고 있다.

#### MyDRC Pro

Hierarchical Design Rule Check

Al geometric angles

Hierarchical or flattened mode DRC

Customizable error messages

Derived layer generation

Support lambda based rule

DRACULA Command Compatible

#### NayNet Pro

Multi-Level Hierarchical Layout Extraction Extract standard SPICE & HSPICE format with model names DRACULA Command Compatible Hierarchical Labeling

Automatically locates any device and net

#### MyLVS Pro

Supports standard industry file formats: SPICE, PSPICE, HSPICE

Detailed discrepancy report and matched device report

Smashing device and reducing CMOS Display discrepancies on LayEd

#### Data Translator (CIF/GDS Pro)

MyChip Station의 Data Translator인 CifGDS는 Standard format인 GDSII는 물론이며 AutoCAD의 DXF, CIF, ANF(Ansys) format을 호환할 수 있으며 원하는 데이터만 분류하여 변환할 수도 있습니다.

#### CIF/GDS Pro

GDSII, CIF and DXF file format의 상호 변환

Create default techfile automatically : techfile없이 GDSII 등의 format file만 있어도 Import 할 경우 자동으로 각 Layer에 맞게 techfile을 생성

Layer Number Modification : GDSII Export 할 때 임시로 GDS의 번호 변경 가능.

참조된 libraries를 포함하여 Export.

사용자가 원하는 Cell과 Layer만 선택하여 Export가능.

grid scale 지원

Object의 vertex수가 일정 개수 이상일 때 자동으로 나눔.

#### MyChip 관련 교재들

무료 다운로드: www.mycad.co.kr

회사명: 셀로코 주식회사

웹주소: http://www.seloco.com/ 전화: 02-3432-1210 E-mail: mycad@seloco.com 주소: 서울시 송파구 송파동 95-55 장원빌딩 3층