반도체설계교육센터 사업은 지식경제부, 반도체산업협회, 반도체회사(삼성전자, 하이닉스반도체, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 세미텍, TowerJazz)의 지원으로 수행되고 있습니다.

# 시스템수준 언어: SystemC & System Verilog

최근 시스템반도체(SoC)가 디지털시스템의 핵심이 되면서 '시스템'이라는 개념을 바꾸고 있다. 하드웨어와 소프트웨어, 다양한 기능의 주변장치들 결합과 통 신 등 시스템의 복잡한 사양을 작성하고 모델링, 설계 및 검증수행을 RTL수준에서 진행하기에는 그 복잡도를 다루기가 매우 어렵다. 이에 '시스템수준'이라고 하는 RTL보다 좀 더 높은 추상화 수준에 적합한 언어에 의해 각 과정을 진행할 필요가 있다. 본 고에서는 시그널, 이벤트, 인터페이스 등과 객체지향개념을 지원하는 SystemC와 SystemVerilog에 대해 간단히 살펴보고자 한다. (관련기사 P04~06 참조)

고화질 멀티미디어 응용과 시스템의 다기능화의 지속적인 요구로 칩 간의 고속 인터페이스 기술은 계속해서 새롭게 발전하고 있다. 고속 인터페이스 기술의 연구는 케이블을 이용한 직렬 링크와 PCB 상의 짧은 전송을 기본으로 하는 병렬 링크로 구분되어 연구되고 있다. 직렬 링크는 고비용 미세공정과 비교적 많 은 전력을 사용하여 넓은 대역폭을 갖는 구리 혹은 광케이블을 통한 20Gb/s 이상의 속도를 달성하기에 이르렀으며, 병렬 링크는 비용 및 저전력과 병렬화의 사이에서 최적의 해답을 위해 다양한 구조로 시도되며 발전하고 있다. 본 고에서는 병렬 링크의 최근 연구 동향에 대해서 살펴보고자 한다. (관련기사 P08~10 참조)

Millimeter-Wave Phased Array System 우리 사회는 1990년대 중반 이후의 인터넷 시대를 거쳐, 이제는 유비쿼터스 멀티미디어 (ubiquitous multimedia) 시대에 들어섰다. 언제 어디서나 원하는 정보를 단순한 텍스트가 아닌 멀티미디어 동영상으로 접하고 있으며, 더 나아가 증강현실 기법을 통해 현실 세계의 공간적 제한을 넘어서려는 시도가 이루어 지고 있다. 기술적인 측면에서 살펴보면, 더 많은 정보의 더 빠른 전송을 요구하는 시대이다. 본 원고에서는 Millimeter-Wave Phased Array System에 대 해 알아보고자 한다. (관련기사 P12~P14 참조)

모바일 Application Processor와 공정의 미세화는 반도체 업계뿐만 아니라 주식시장에서도 초미의 관심사가 되고 있다. 모바일 CPU를 석권하고 있는 ARM 의 CPU 개발 일정에서 알 수 있듯이 공정의 미세화는 고성능과 저전력 구현을 위한 필수 기반기술이다. 생산성을 고려한 설계를 주로 Layout 설계관점에서 다루었는데, DFM 규칙은 생산자에 의해 주도되므로 설계자 입장에서는 DFM의 효과 보다는 적용의 용이성에 더 관심을 갖게 된다. 본 고에서는 생산성을 고 려한 설계에 대해 살펴보고자 한다. (관련기사 P16~P19 참조)

# June | 2012

| MPW (Multi-Project Wafer) |                               |                            |                |                                       |                                |                                |                                                                                   |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

|---------------------------|-------------------------------|----------------------------|----------------|---------------------------------------|--------------------------------|--------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|---------------------------------------------|---------------|----------------|-------------------------|

| MPW 신청 현황   MPW 칩 제작 현황   |                               |                            |                |                                       |                                |                                |                                                                                   |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

|                           |                               |                            |                |                                       |                                |                                |                                                                                   |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

|                           | M/H<br>0.18                   | 4.5×4mm×20                 | 20             | 4.5×4mm×20                            | 2012.<br>5.14                  | 2012<br>9.3                    | BD마감                                                                              | 105회<br>(11-08)                                                                                                                                                                     | 동부<br>0.11     | 29    | 5x2.5m² x 21<br>2.5x2.5m² x 8               | 2012.<br>1.10 | 제작완료           | -Die:2.8<br>-PKG:4.27   |

| 111회                      | M/H<br>0.35<br>동부<br>0.35BCD  | 5x4m²x20<br>5x5m²x3        | 20<br>7        | 5x4m20<br>5x2,5m24<br>2,5x2,5m23      | 2012<br>5.14<br>2012<br>5.24   | 2012<br>9.3<br>2012            | :5.25<br>BD마감                                                                     | 106회<br>(11-09)                                                                                                                                                                     | 삼성<br>0.13     | 43    | 4×4m² × 43                                  | 2012.<br>3.9  | 제작완료           | -Die:4.20<br>-PKG:5.24  |

| (12–4)                    | TJ0.18<br>CIS                 | 5x5mm²x1                   | 2              | 5x2,5mm22                             | 2012.<br>5.7                   | 8.30<br>2012<br>9.14           | :5.24<br>BD전달<br>:5.18<br>BD마감                                                    | 107회<br>(11-10)                                                                                                                                                                     | M/H<br>0.18    | 24    | 4.5x4m² x 15<br>4.5x2m² x 6<br>2.25x2m² x 3 | 2012.<br>4.10 | Package<br>제작중 | -Die:5.9<br>-PKG:6.10   |

|                           | TJ0.18<br>BCD<br>삼성<br>65nm   | 5x5m²x2<br>20개서버           | 20             | 5x5m²x2<br>5x5m²x23                   | 2012.<br>5.14<br>2012.         | 2012<br>9.21<br>2012           | :5.14<br>BD마감                                                                     |                                                                                                                                                                                     | M/H<br>0.18    | 20    | 4.5×4m² × 20                                | 2012.<br>6.4  | 제작중            | -Die:7.21               |

| 112회<br>(12-5)            | 65nm<br>동부<br>0.18BCD         | (4x4mm²)<br>5x5mm²x2       | 20<br>서버<br>4  | 5x2,5mmx4                             | 6.4<br>2012<br>6.20            | 11.9<br>2012<br>9.26           | :6.2<br>BD마감<br>:6.20                                                             | 108회                                                                                                                                                                                | 동부<br>0.35BCD  | 16    | 5x2.5m² x 2<br>2.5x2.5m² x 8                | 2012.<br>5.30 | Package<br>제작중 | -Die: 5.15<br>-PKG:6.10 |

| 113호<br>(12-6)            | 동부<br>0.35BCD                 | 5x5m²x3                    | 8              | 5x2.5mmx4<br>2.5x2.5mmx4              | 2012.<br>7.4                   | 2012                           | .0.20<br>설계중                                                                      | (12-1)                                                                                                                                                                              | TJ0.18<br>SiGe | 4     | 2,5x2,5m² x 4                               | 2012.<br>7.2  | 제작중            |                         |

| 44.4=1                    | 동부<br>0.18BCD                 | 5x5mm2                     | 2              | 5x5m²x2                               | 2012<br>8.8                    | 2012<br>11.14                  |                                                                                   |                                                                                                                                                                                     | TJ0.18<br>RF   | 8     | 2.5x2.5m² x 4                               | 2012.<br>7.5  | 제작중            |                         |

| 114회<br>(12-7)            | M/H<br>0.18<br>삼성             | 4.5x4mix20<br>4x4mix48     | 19<br>31       | 4.5×4m²×19<br>4×4m²×31                | 2012.<br>8.13<br>2012          | 2012<br>12.3<br>2013           | 설계중                                                                               | 109회<br>(12-2)                                                                                                                                                                      | 삼성<br>0.13     | 40    | 4×4m² × 40                                  | 2012.<br>8,3  | 제작중            |                         |

| 115호 <br>(12-8)           | 삼성<br>0.13<br>동부<br>0.18BCD   | 5x5m²x2                    | 5              | 5x2.5mmx3<br>2.5x2.5mmx2              | 2012.<br>8.31<br>2012.         | 2013.                          | 모집마감                                                                              | 110회                                                                                                                                                                                | 동부<br>0.35BCD  | 9     | 5x2.5m² x 2<br>2.5x2.5m² x 7                | 2012.<br>7.12 | 제작중            |                         |

| (12-6)                    | TJ0.18<br>CIS                 | 2.5x2.5m²x4                | 4              | 2.5x2.5mmx2<br>2.5x2.5mmx4            | 9.6<br>2012<br>10.15           | 1.4<br>2013.<br>2.22           |                                                                                   | (12-3)                                                                                                                                                                              | 동부<br>0.11     | 29    | 5x2.5m² x 22<br>2.5x2.5m² x 7               | 2012.<br>8.1  |                | DB전달<br>:5.15           |

| 116회<br>(12-9)            | TJ0.18<br>BCD<br>TJ0.18<br>RF | 5x5m²x2<br>2.5x2.5m²x4     | 2              | 5x5mm2<br>2,5x2,5mm23                 | 2012<br>10.22<br>2012<br>10.22 | 2013.<br>2.29<br>2013.<br>2.29 | 모집마감                                                                              | * M/H = 매그나칩/하이닉스, TJ = TowerJazz<br>* 우선/정규모집에서 마감될 경우 후기모집은 진행되지 않음.<br>* Die-out 일정은 Diechip 제작완료 기준임, Package는 Die-out후 4주 이상 소요됨.<br>* MPW 참여 일정 및 방법은 홈페이지(www.idec.or.kr) 참조 |                |       |                                             |               |                |                         |

| (12–9)                    | RF<br>동부<br>0.35BCD           | 5x2.5mmx6                  | 7              | 5x2.5mmx3<br>5x2.5mmx4<br>2.5x2.5mmx3 | 10.22<br>2012<br>10.10         | 2.29<br>2013<br>1.16           |                                                                                   |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

|                           | 동부<br>0.11                    | 5x2.5mm230                 | 28             | 5x2.5mmx23<br>2.5x2.5mmx5             | 2012.<br>10,2                  | 2013.<br>2.6                   | 후기모집 * 위의 내용은 5.25 기준임.<br>:~7.1<br>3, 2013년 MPW 공정 및 일정은 2012년 11월 이후 공지될 예정입니다. |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

| 117회<br>(12-10)           | M/H<br>0 <u>.</u> 18          | 4.5x4mix20                 | 16             | 4.5x4m²x16                            | 2012.                          | 2013.<br>3.4<br>2013.          | 후기모집<br>:~81                                                                      | 3, 2013년                                                                                                                                                                            | MPW 공정         | 및 일정은 | 2012년 11월 이후 공                              | 시될 예정입니[      | -t.            |                         |

|                           | M/H<br>0.35<br>삼성<br>65nm     | 5×4㎡×20<br>20개서버<br>(4×4㎡) | 10<br>17<br>서버 | 5x4nnix10<br>4x4nnix18                | 2012<br>11.12<br>2012<br>11.26 | .12 3.4                        | . *0.1                                                                            |                                                                                                                                                                                     |                |       |                                             |               |                |                         |

\* 2012년 MPW 중 116~117회의 일부 공정에 대한 후기 모집 외 모든 공정의 모집이 마감됨.

# IDEC, 마스크(MASK) 무상 배포

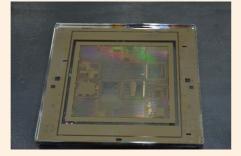

반도체설계교육센터에서는 마스크(Mask)를 교육적 효과를 위해 신청을 받아 무상으로 배포합니다.

마스크(Mask)란 반도체 소자 혹은 집적회로의 구조를 크롬이 칠해진 유리판 위에 형성한 것을 말하며, 사진술을 이용하여 유리판 구조를 웨이퍼(Wafer)상에 복사함으로써 반도체 에 회로가 인쇄되게 된다. 웨이퍼는 사진 인화지, 마스크는 필름에 비유할 수 있으며 좋 은 제품을 만들기 위해서는 원판인 마스크의 신뢰성과 정확성이 수반되어야 한다.

● 신청 및 문의: 이의숙 (042-350-4428, yslee@idec.or.kr)

마스크(Mask) 모습

# 2012년 6월 교육프로그램 안내

수강을 원하는 분은 IDEC홈페이지(www.idec.or.kr)를 방문하여 신청하시기 바랍니다.

| 장소 강의일자 강의제목                                                                                                          |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| 영소 성의실시 성의세속                                                                                                          | 분류 |

| 충북대 IDEC 6월 25-29일 Hardware/Software Issues and Applications of Multicores for Future Embedded Systems                | 설계 |

| 전북대 IDEC 6월 26-27일 차량용 임베디드 시스템                                                                                       | 설계 |

| 차량환경 및 노이즈에 강한 고신롸성 회로 설계<br>한양대 IDEC 6월 28일 (차량용 고신뢰성 low-jitter 노이즈 클록 신호 발생기)<br>/ 차량용 클록의 Analog Sub-Block 설계 이슈들 | 설계 |

| KAIST IDEC 6월 28-29일 Verilog HDL을 활용한 IP 설계                                                                           | 설계 |

- 강좌일: 6월 25일-29일

- 강좌 제목: Hardware/ Software Issues and Applications of Multicores for Future **Embedded Systems**

- 강사: Prof. Ben Lee (School of Electrical Engineering and Computer Science)

# [ 강좌개요 ]

| 01 (0.1: 1)                                                 | 0 1 1                                                                                                                                                                                                              | 5.1                                          |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Class(Subject)                                              | Content                                                                                                                                                                                                            | Date                                         |

| Part 1:<br>Hardware<br>Aspects of<br>Embedded<br>Multicores | <ul> <li>Parallel Computers</li> <li>ARM</li> <li>Unique Features of ARM</li> <li>ARM MPCore</li> <li>A Crash Course on<br/>SuperScalar Processors</li> <li>Synchronization</li> <li>Cache Coherence</li> </ul>    | Monday,<br>June 25 ~<br>Tuesday,<br>June 26  |

| Part II: Software<br>Aspects of<br>Embedded<br>Multicores   | <ul> <li>Introduction</li> <li>Shared-Memory</li> <li>Programming</li> <li>Pthreads</li> <li>OpenMP</li> <li>Other Issues</li> </ul>                                                                               | Wed.,<br>June 27                             |

| Part III: Low<br>Power Issues in<br>Embedded<br>Multicores  | <ul> <li>Introduction</li> <li>Architectural Low</li> <li>Power Techniques</li> <li>Dynamic Voltage &amp;</li> <li>Frequency Scaling</li> <li>DVFS and Embedded</li> <li>Multicores</li> <li>MPCore IEM</li> </ul> | Thursday,<br>June 28 ~<br>Friday,<br>June 29 |

# [ 강의수준 ] [ 강의형태 ]

· 이론+실습 · 초중급

- 강좌일: 6월 26일-27일

- 강좌 제목 : 차량용 임베디드 시스템

- 강사: 이종열 교수(전북대)/ 우균 교수(부산대)

# [ 강좌개요

본 강의에서는 일반적인 차량용 임베디드 시스템에 대한 이론을 다룬다. 또한 국산 임베디드 프로세서인 Core-A에 대하여 학습하고, Core-A 를 이용한 차량용 임베디드 시스템에 대하여 학습한다. 주요 강의 내용 은 다음과 같다.

- Core-A 프로세서의 개요 및 구조

- Core-A 개발 환경

- Genivi 차량용 infotainment platform 소개

- Genivi 차량용 infotainment platform를 이용한 IVI 개발

# [ 수강대상 ]

[ 강의형태 ]

· 이론 · 석박사 과정, 관련 회사원

# [ 사전지식, 선수과목 ]

컴퓨터구조, 디지털로직, 컴퓨터 언어

- 강좌일: 6월 28일

- 강좌 제목 : 차량환경 및 노이즈에 강한 고신뢰성 회로 설계(차량용 고신뢰성 low-iitter 노이즈 클록 신호 발생기)/ 차량 용 클록의 Analog Sub-Block 설계 이슈들

- 강사 : 이강윤 교수(성균관대)

# [ 강좌개요 ]

PLL은 통신에서 클록을 생성하기 위해서 널리 사용되고 있는 핵심적인 블록중의 하나이다. 본 강좌에서는 차량환경 및 노이즈에 강한 고 신뢰 성 PLL의 동작원리, VCO, Charge Pump, Divider 등의 구성 회로 및 설계 이슈 등을 다룬다.

# [ 수강대상 ]

· 석박사 과정, 관련 회사원

# [ 강의수준 ] ㆍ초급

[ 강의형태 ]

· 이론

# [ 사전지식. 선수과목 ]

· 전자회로 1, 2

- 강좌일: 6월 28-29일

- 강좌 제목: Verilog HDL을 활용한 IP 설계

- 강사: 김지훈 교수(충남대)

# [ 강좌개요 ]

Verilog HDL의 기초 및 효율적인 IP설계를 위한 방법론

- Verilog HDL 기초

- IP 설계시 고려사항

- Coding Guideline for Synthesis

# [ 수강대상 ]

· 학부생 및 석사과정

# [ 강의수준 ]

·초중급

[ 강의형태 ] · 이론+실습

# [ 사전지식, 선수과목 ]

· 논리회로 및 컴퓨터구조

<sup>\*</sup> 문의:이의숙(042-350-4428 yslee@idec.or.kr)

# 시스템수준 언어: SystemC & SystemVerilog

# 충북대 전자정보대학 반도체공학과

송기용 교수

연구분야: SoC 설계·검증, SystemC 모델링

E-mail: gysong@cbnu.ac.kr http://bnadi.cbnu.ac.kr/~gysong

# 충북대 전자정보대학 반도체공학과

오영진 박사 과정

연구분야: SystemVerilog기반 하드웨어 검증 플랫폼, SystemC기반 설계

E-mail: goodmen913@cbnu.ac.kr

# 江东东岭社出

# 서론

# 시스템수준 언어의 필요성

최근 시스템반도체(SoC)가 디지털시스템의 핵심이 되면서 '시스템'이라는 개념을 바꾸고 있다. 고전적인 시스템의 개념은 마이크로프로세서, 메모리 칩, 아날로그 부품 그리고 기타 ASIC과 같은 개별적인 부품들을 모아 하나의 결과를 산출하는 것이었다. 이러한 시스템의 설계는 시스템설계 전문가가 하드웨어와 소프트웨어로 개발 부분을 분할하고, 이에 따른 사양이 결정되면 RTL 수준으로 설계하는 방식으로 진행되었다. 이때 HDL은 매우 적절한 선택이다[1].

그러나 시스템반도체는 다수 프로세서와 DSP, 특정기능의 수행성 능 향상을 위한 하드웨어 부분과 주변 제어장치들을 버스를 통해 연결하고, 각 모듈은 자체적으로 작동하며 버스의 프로토콜에 따라 통신을 하게 된다. 이는 필연적으로 하드웨어와 결합할 소프트웨어의 필요성을 증대시키고, 하드웨어를 제어하는 소프트웨어의 복잡성을 증가시킨다.

하드웨어와 소프트웨어, 다양한 기능의 주변장치들 결합과 통신 등 시스템의 복잡한 사양을 작성하고 모델링, 설계 및 검증수행을 RTL수준에서 진행하기에는 그 복잡도를 다루기가 매우 어렵다. 이 에 '시스템수준'이라고 하는 RTL보다 좀 더 높은 추상화 수준에 적합한 언어에 의해 각 과정을 진행할 필요가 있다. 본 고에서는 시 그널, 이벤트, 인터페이스 등과 객체지향개념을 지원하는 SystemC 와 SystemVerilog에 대해 간단히 살펴보고자 한다.

# 본론

### SystemC

SystemC는 상위수준 언어인 C/C++에 하드웨어 설계개념을 도입한 형태로, 개발대상 시스템이나 모듈의 구조탐색, 성능모델링을 위한 TLM을 포함한 여러 추상화 수준의 모델링, 또는 초기 소프트웨어 개발을 위한 가상 프로토타입 작성에 적합한 객체지향 언어이다.

SystemC는 하드웨어 모델링을 위해 모듈 내부에서의 모듈 사례 (instantiation)를 통한 계층화, SC\_METHOD, SC\_THREAD와 SC\_CTHREAD를 통한 프로세스 수행의 동시성, sc\_int(〉, sc\_logic 등의 하드웨어 데이터타입, sc\_time, sc\_clock 클래스가 제공하는 시간 모델 등의 개념을 포함하는 C++ 클래스 라이브러리

와 사건구동(event-driven) 방식의 시뮬레이션 커널로 구성되며, 하드웨어 모듈, 소프트웨어 코드, 그리고 이 둘이 결합한 시스템을 통합 설계할 수 있는 환경을 제공한다.

SystemC를 사용한 RTL 수준의 설계도 가능하지만 RTL보다 높은 추상화 수준에서 하드웨어, 소프트웨어 또는 이 둘이 결합한 시스템의 모델링에 주로 이용된다. Doulos 사의 조사결과(2)에 의하면 SystemC는 성능모델링(68%), 구조탐색(68%), TLM(56%), 하드웨어-소프트웨어 통합시뮬레이션(56%) 등에 주로 사용되고 있다.

### SystemVerilog

SystemVerilog는 Verilog HDL에 객체지향 개념을 도입한 형태로, 연산자 오버로딩, 인터페이스, IPC(interprocess communication)와 같은 개념이 추가되었으며, constrained-random stimuli generation, functional coverage, assertion 등이 테스트벤치 작성에 이용되도록 제공된다. 이러한 확장을 통해 SystemVerilog는 단일언어로 시스템의 설계 및 검증기능을 수행할 수 있다. 또한 DPI(Direct Programming Interface)를 이용하여 System Verilog 테스트벤치에서 SystemC TLM에 접근할 수 있어 두 블록 간의 동시 시뮬레이션이 가능하다.

# TLM(Transaction-Level Modeling)

행위수준 모델링이 기능의 추상화를 끌어올리는 반면, TLM은 제어 와 자료흐름 등 정보교환의 하위수준 세부내용을 메소드에 은닉하 여 블록 간 통신의 추상화를 끌어올린다. TLM은 모듈의 처리기능 과 그들 사이의 통신을 분리하는 것으로 데이터 통신의 실제 구현 보다 데이터 전송의 기능성을 강조한 형태이다[1]. 모듈은 채널에 구현된 인터페이스 함수를 호출하여 전송을 요구하게 된다.

이처럼 모듈 간 통신을 함수호출 방식으로 진행하고, 기능의 정확성에 비중을 두어 구조적인 측면에 집중하지 않는다. 예를 들면 버스 설계 시 버스가 지원하는 읽기/쓰기 방식에 대한 여러 가지 전송형태(단일전송, 일괄전송 등)를 모델링하며 버스에 연결되는 실질적인 비트 폭이나 모듈의 핀 등에 대한 구체적인 기술은 하지 않는

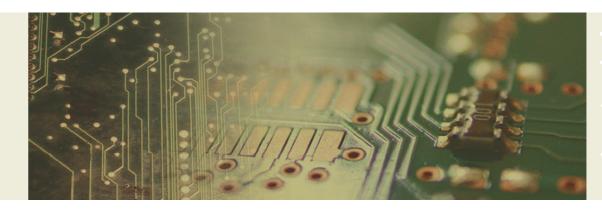

마이크로프로세서와 메모리, 기타 주변소자가 버스로 연결된 경우의 일괄전송 타이밍 도표를 가지고 추상화 수준, 즉 상세정도를 비교해 보면[3]

하나의 일괄전송이 버스 사이클 타임의 설정 등으로 상세정도가 사이클 상세수준이 되면, 각 클럭-사이클에서의 전달이 이벤트가 되며, 버스사양이 충분히 구체화하면 각 신호 트랜지션에서 이벤트가 발생한다. 즉 상세 정도가 심화할수록 단위전송이 세분화되는 형태를 보이게 된다.

# SystemC TLM

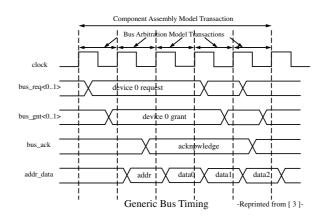

계층채널의 한 경우로 두 개의 마스터와 두 개의 슬레이브가 연결되는 간단한 기능의 버스를 모델링하여 TLM의 예를 보인다[4].

마스터는 버스전송을 개시할 수 있으며, 전송요청이 버스 내부의 큐에 저장되면, 중재기에 의해 사전에 설정된 우선순위에 따라 처리되어 슬레이브에 전달되고, 지정된 슬레이브가 정상적으로 응답하면 해당 전송이 완료된다. 클럭이 연결되지 않은 슬레이브는 단일 사이클 내에 읽기 또는 쓰기 동작 수행이 가능한 '빠른' 메모리모델의 경우이고, 클럭이 연결된 슬레이브는 읽기 또는 쓰기 동작수행에 다수의 클럭 사이클을 필요로 하는 '느린' 메모리모델의 경

우로 필요한 클럭 수를 설정할 수 있다[1]. 버스는 포트를 통한 인 터페이스 함수호출로 접근되고, sc\_event&를 통해 포트에 감응 (sensitive)하는 모듈의 프로세스를 기동시킨다. 위 그림의 버스는 제어신호, 자료형 및 타이밍 등을 고려한 구체화 과정을 거쳐 SystemC RTL로 구현되며, 이때 어댑터, 컨버터 또는 wrapper의 삽입이 필요하게 된다.

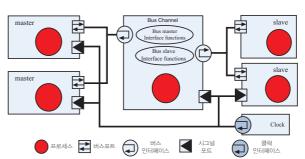

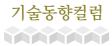

# SystemVerilog TLM & BFM

SystemVerilog는 TLM을 동작적 모델링(behavioral modeling) 의 부가적인 것으로 정의 한다. SystemVerilog의 TLM은 인터페이스를 통해 데이터 흐름과 제어의 상세내용을 은닉하여 정보교환의 추상화 수준을 높이며, 인터페이스와 태스크 호출 매커니즘은 TLM의 작성을 용이하게 해준다. TLM이 하드웨어 설계로 구체화하려면 통신프로토콜을 구현하고 하드웨어와 신호를 교환하는 BFM이 RTL모듈에 연결되어야 한다. Intel Multibus를 기본으로 하는인터페이스를 이용하여 RTL로 구현된 메모리모듈과 연결되는 BFM의 개략적 형태를 아래 그림에서 살펴본다[5].

인터페이스를 선언 및 정의하고 TLM과 PLM(Pin-Level-Model) 버스로 생성한 후 이를 각 모듈에 맵핑시킨다. 이는 System Verilog가 Verilog의 확장형태로 RTL수준의 모듈에 어떠한 변경

이나, 추가적인 코드작성 없이 바로 연결할 수 있기 때문이다

# SystemC 와 SystemVerilog의 연계

SystemVerilog의 DPI기능을 이용하여 SystemC와 System Verilog로 구현된 객체들을 연계할 수 있다. 이러한 연계의 핵심은 SystemVerilog의 태스크로부터 직접 SystemC 메소드를 호출하 거나 반대로 SystemVerilog 태스크를 SystemC 메소드가 직접 호출하는 것이다. DPI는 설계자가 C/C++/SystemC 기능을 SystemVerilog 모듈에 포함할 수 있도록 하는 인터페이스로 2개 의 레이어로 구성되며 기존의 C 코드를 쉽게 재사용할 수 있도록

C에서 구현된 기능은 SystemVerilog의 import "DPI" 선언을 이 용하여 호출될 수 있고, SystemVerilog로 구현된 기능을 C 모듈 에서 사용하기 위해 export "DPI" 선언을 통해 호출할 수 있다[6].

SystemVerilog DPI는 다음과 같은 방식으로 SystemC에 접근한

- SystemC 모델의 입출력 포트를 나타내기 위한 Verilog shell모듈을 생성한다.

- DPI와 SystemC 모델 사이에 값을 전달하는 C 함수를 만든다.

- Verilog shell 모듈에서 SystemC 모델을 제어하는 C 함수를

다음은 DPI를 사용하는 예를 간단히 보인 것이다[8].

이 경우 유의할 점은 다음과 같다.

- slave\_write C 함수는 SystemVerilog 함수의 내부에서 호출 되며, 인자들은 값에 의해 전달되어야 한다.

- ■import 되는 함수의 인자들은 'const'로 선언되어야 한다. DPI의 import/export 함수는 모듈, 프로그램, 인터페이스 등 SystemVerilog 함수가 선언되는 모든 영역에서 선언될 수 있 며 ero simulation time에 수행된다.

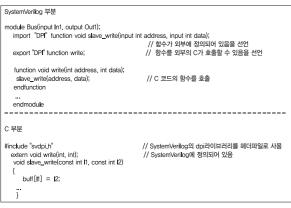

이러한 기능을 통해 아래 그림[2]과 같이 SystemC TLM을 SystemVerilog 테스트벤치에 결합하여, 하드웨어의 검증과정에서 SystemC TLM을 참조모델로 사용할 수 있다

SystemC는 C++에 하드웨어 개념을 도입한 경우이고, System Verilog는 Verilog HDL에 OOP 개념을 도입한 경우이다. 상위수 준에서의 시스템 모델링을 위하여는 SystemC가 우선 선택될 것이 고. 구현된 모델은 설정되어 있지만 복잡한 구체화 과정을 거쳐 SystemC RTL에 이르게 된다.

SystemVerilog의 경우 TLM의 태스크 내부에 함수호출과 신호대 기. 할당 등이 동시에 나타나게 되어 구조화 관점에서 다소 혼란스 러울 수 있다. SystemC 또는 SystemVerilog를 이용하여 시스템 모델링, 구체화 과정을 통한 RTL구현 및 검증플랫폼 구축이 가능 하며 SystemVerilog의 DPI를 이용하여 각 언어에 기반을 둔 모듈 을 결합할 수 있다.

참고로, HDL은 델타 타임의 이해에 어려움이 있으며 SystemC 할 당은 회로의 wire에 해당하는 채널 sc signal 에서의 임시저장을 통한 평가와 경신 과정의 이해에 어려움이 따른다. 이는 사건구동 시뮬레이터에 의한 하드웨어 모델링을 위한 전제라 할 수 있다.

# Reference

- [1] 국일호 역. "SystemC를 이용한 시스템 설계". 에이콘. (2003). Thorsten Grotker, Stan Liao, Grant Martin, Stuart Swan, "System Design with SytemC", Kluwer Academic Publishers

- [2] http://www.soccentral.com/results.asp?categoryID=488

- [3] David C. Black and Jack Donovan, "SystemC: From The Ground Up", Springer, (2004)

- [4] 기안도, "SystemC 시스템모델링 언어", IDEC 교재개발 시리 35, 대영사.(2005)

- [5] Stuart Sutherland, Simon Davidmann and Peter Flake. "SystemVerilog for Design (2nd Edition): A Guide to Using System Verilog for Hardware Design and Modeling", Springer Science+Business Media, LLC(2006)

- [6] Myoung-Kenu You, Gi-Yong Song. 'SystemVerilog-ased Verification Environment Employing Multiple Inheritance of SystemC', IEICE Trans. Japan(2010), Vol E-3A, No5, pp. 989-992

- [7] Stuart Sutherland, 'Integrating SystemC Models with erilog and SystemVerilog Models Using the SystemVerilog Direct Programming Interface', SNUG, USA, Boston, (2004).

- [8] http://www.asic-world.com/systemverilog/tutorial.html

# 서울대학교 SoC설계기술센터(CoSoC) / 반도체설계교육센터(IDEC)

# 제8차 SoC 설계 경진대회

**꾸 회** 지식경제부

**쭈 관** 서울대학교 SoC설계기술센터(CoSoC), 반도체설계교육센터(IDEC)

# 참가방법

♣ 국내 대학의 SoC 관련 연구실에서 지도교수의 추천을 받은 학생들이 팀을 구성하여 참가

# 경진부문

- ♣ 부문 1 : SoC 플랫폼 이용 또는 HW IP(analog 또는 digital) 설계

- ▶ 참기팀은 최종적으로 보드상에서 FPGA 또는 Chip 레벨의 시연을 하여야 함

- ▶ 설계결과물의 동작여부 뿐만 아니라 검증 방법론을 비중 있게 심사함

- ♣ 부문 2: FPGA를 이용한 Connect 6 player 설계 경연

- ▶ 육목게임의 일종인 Connect 6 player를 구현하여 1:1 대전을 통해 승패로 우수자 선정

- ▶ 올해 12월에 서울대학교 호암교수회관에서 개최될 FPT' 12(http://icfpt2012.blogspot.com)의 DesignCompetition과 연계하여 진행

# 진행일정

| 일정(2012년)   | 부문 1                       | 부문 2            |  |  |  |

|-------------|----------------------------|-----------------|--|--|--|

| 6월 18일 (월)  | 경진대회 설명회 및 Connect 6 데모 시연 |                 |  |  |  |

| 7월 1일(일)    | 참가 신청 및 설계 제안서 제출 마감       | 참가 신청 마감        |  |  |  |

| 10월 20일 (토) | -                          | 포스터 논문 제출(영문)   |  |  |  |

| 10월 26일 (금) | 최종 보고서 제출                  | Connect 6 예선 대회 |  |  |  |

| 11월 20일 (화) | 발표 심사 팀 선정 통보              | -               |  |  |  |

| 11월 23일 (금) | 발표심사                       | Connect 6 결선 대회 |  |  |  |

| 11월 30일 (금) | 시성                         | 씱               |  |  |  |

♣ 부문별로 우수팀을 선정 하여 지식경제부 장관상 및 우수상, 장려상을 시상함

# 문 의

- ♣ 유성목 (yooka88@sdgroup.snu.ac.kr/☎ 02-880-5457)

- ♣ 설계 제안서 양식과 게임의 룰 및 기타 자세한 내용은 서울대학교 SoC설계기술센터의 포털 홈페이지(http://soc.snu.ac.kr/portal) 참고

# 병렬 링크 설계 연구 동향

# 포항공과대학교 전자전기공학과

심재윤 교수

연구분야: 고속/저전력 아날로그 회로 설계

E-mail: jysim@postech.ac.kr http://analog.postech.ac.kr/

いななられる

# 서론

고화질 멀티미디어 응용과 시스템의 다기능화의 지속적인 요구로 칩간의 고속 인터페이스 기술은 계속해서 새롭게 발전하고 있다. 고속인터페이스 기술의 연구는 케이블을 이용한 직렬 링크와 PCB 상의짧은 전송을 기본으로 하는 병렬 링크로 구분되어 연구되고 있다. 직렬 링크는 고비용 미세공정과 비교적 많은 전력을 사용하여 넓은 대역폭을 갖는 구리 혹은 광케이블을 통한 20Gb/s 이상의 속도를 달성하기에 이르렀으며, 병렬 링크는 비용 및 저전력과 병렬화의 사이에서 최적의 해답을 위해 다양한 구조로 시도되며 발전하고 있다.

특히 프로세서 및 메모리 인터페이스로 대표되는 병렬 링크는 최근의 소형 스마트 전자기기의 급속한 발전으로 빠른 속도와 낮은 전력 소모를 동시에 달성하여야 하는 도전에 직면하여 과거의 단순한 single—ended 신호 전송을 기반을 둔 단순한 방법에서 탈피하여 직렬 링크 회로의 병렬 링크로의 최적화 도입과 패키징 및 공정 기술의 개발까지 포함한 다양한 기술의 융합이 시도되고 있다. 이 글에서는 병렬 링크의 최근 연구 동향에 대해서 살펴본다.

### 본돈

고속 저전력 병렬 링크에서 일반적으로 사용되는 성능의 지표는 Gb/s당 전력 소모로 나타낸다. 2007년 International Solid State Circuits Conference (ISSCC)에서 Rambus 사에 의해 기존의 지표를 1/3 이하로 줄인 2mW/Gb/s 대의 성능이 처음으로 발표되었다 [1]. 여기서 사용된 회로 기술들은 기본적으로 이전에 제안되었거나 조금씩 변형된 것들로 이루어져 있으나 저전력으로 고속 데이터 전송을 한다는 목표로 각 부분을 최적화하여 전체를 구성한 하나의 최적화 해법을 제시한 것으로, 이후에 발표된 대부분의 저전력 병렬 인터페이스 연구에서 참고되었다. 현재는 미세공정과 회로 기술의 발전으로 비슷한 구조로 1mW/Gb/s 수준까지 발표된 바가 있다 [2].

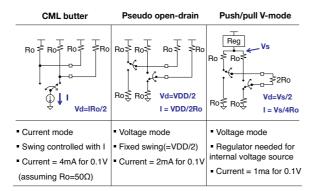

# 출력 버퍼

병렬 링크의 설계에서 가장 중요한 회로블록 중 하나는 출력 버퍼로 서, 정합, 출력 전압 폭, 속도, 소모전력 등의 요구에 따라 설계 단계 있다. 에서 적합한 선택이 필요하다. 그림1에 differential signaling에서 병렬 정합 구조를 갖는 출력 버퍼 회로들을 보였다. 전류 모드 버퍼 그림 2는 전압 모드 버퍼보다 전압 변동폭을 전류만으로 쉽게 조절할 수 있으로도는 장점이 있으나 [3], 동일한 출력 전압 폭을 유지하는데 전압모드 버퍼에 비해 2배의 높은 전력을 소모하므로 저전력 소모가 중요한 병 모드에 렬 인터페이스에서는 전압 모드 버퍼가 더 많이 채택되고 있다. 전압 수 있다 모드 버퍼 중 pseudo open—drain 방식은 일반적인 CMOS 버퍼와 기 때문 비슷하고 간단한 형태를 보이고 있어 single—ended 구조로 현재 고

속 메모리인 그래픽 DRAM 인터페이스에서 널리 사용되고 있다 [4, 5]. 최근 연구가 활발히 진행되는 differential signaling을 이용한 저전력 고속 병렬 인터페이스에서는 전압 변동폭을 줄일 수 있도록 온칩 regulator를 추가한 저전압 push-pull 출력 버퍼를 사용한다 [1, 2, 6]. 이 방법은 같은 전압 변동 폭을 생성하기 위해서 전력 소모를 pseudo open-drain 방식에 비해서도 절반으로 줄일 수 있어 병렬 정합을 유지하는 최소 전력 소모 버퍼로서 최근 대부분의 연구에서 채택되고 있다.

그림 1. 출력 버퍼의 종류

# 클럭 포워딩

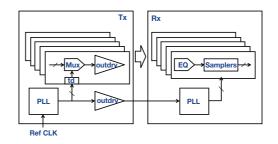

채널이 하나밖에 없는 직렬 링크와 달리 여러 개의 채널을 갖는 병렬 링크에서는 어떻게 효율적으로 각 채널에 클럭 신호를 입력하고 채널 간의 skew를 어떻게 처리하는가가 병렬 링크의 세부적인 구조를 결정짓는다고 할 수 있다. 병렬 링크는 PCB와 같은 짧은 거리에서의 데이터 전송을 목표로 하여 송신단의 주파수 정보를 수신단으로 보낼수 있는 클럭 포워딩 구조를 채용한다. 이 중 소스 동기화 (Source synchronous) 방법은 비교적 복잡하지 않은 제어 회로로 전력 소모를 최소화하면서도 수 Gb/s 영역에서도 잘 동작하여 널리 사용되고 이다

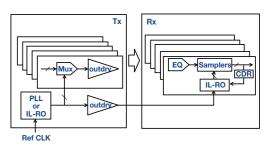

그림 2에서 보인 바와 같이 PLL은 송신부와 수신부에 각각 하나씩만 으로도 가능하며 마스터에 해당하는 칩에만 각 채널별로 미세하게 데이터 송수신 타이밍을 조절할 수 있는 지연회로(td)를 두고 트레이닝 모드에서 피드백을 통해 이를 조절함으로써 채널당 skew를 제거할 수 있다. 슬레이브 칩에는 별도의 위상 감지 및 제어 회로를 두지 않기 때문에 슬레이브에 해당하는 고속 메모리 등에서 선호하는 방식이다 [6]

그림 2. 마스터 제어형 source synchronous 병렬 링크

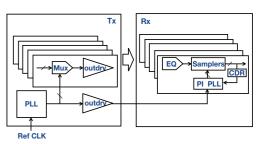

최근에는 병렬 링크에 직렬 링크의 데이터 복원 회로 방법을 최적화하여 적용하는 연구가 활발하게 진행되고 있다. Source synchronous 방식에서는 트레이닝 구간 외에는 위상 오차를 수정할 수 없는데 반해, 수신단에서 직렬 링크에서 사용되는 clock data recovery (CDR) 회로를 채용하여 채널 간 skew를 제거하는 것이다 [1-3, 7, 8]. 클럭 포워딩에 의해 주파수가 이미 주어진 상태이므로 위상 보간기 (phase interpolator, PI)가 포함된 PLL로 채널별로 데이터 복원 클럭의 위상만을 조절하여 채널 간 skew를 제거할 수 있다. 이를 위해서는 각 수신 채널에 개별 CDR 혹은 이에 상응하는 위상 제어 수단이 할당되어야 하므로, 비용과 전력 소모에서의 증가를 최소화하기 위해 위상 보간 방식을 pulsed CDR [8] 또는 sub-rate CDR[3]로 불리는 주기적인 CDR 동작으로 전류의 소모를 최소화한다

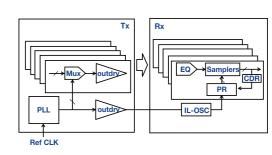

최근에는 전통적인 방식의 PLL 대신에 oscillator만 사용하고 이 oscillator가 외부에서 입력되는 기준 클럭의 천이 정보에 위상을 고정할 수 있는 수단을 구비하여 주파수 고정을 시키는 injection locked oscillator (IL-OSC)를 이용한 클럭 생성 방식도 제안되고 있다. 그림 4에 IL-OSC를 이용한 병렬 링크 구조의 예를 보였다[3]. 수신단에서 하나의 IL-OSC가 PLL과 같이 입력 클럭의 잡음을 필터링함과 동시에 주파수 정보를 추출하여 개별 채널에 제공하면, 국소적으로 CDR이 phase rotator (PR)의 제어를 통해 채널 간 skew를 제거하게 된다.

CDR이 위상을 감지하기 위해서는 여러 개의 위상이 필요한데 IL-OSC는 일반적으로 하나의 위상만 제공하므로 PR에 여러 개의 위상을 생성할 수 있는 별도의 회로가 추가되어야 한다 [3]. 그림 5는 이러한 단점을 보완하기 위해 여러 개의 위상을 생성할 수 있는 ring oscillator를 injection—locked ring oscillator (IL—RO)로 구성하여

각 채널당 하나씩 할당하여 IL-RO의 출력이 바로 CDR을 구동할 수 있게 한다 [9]. IL-RO가 채널당 하나씩 필요하나 PLL보다 간단하여 크기와 전력 소모에 장점이 있다.

그림 3. Local CDR을 채용한 병렬 링크

그림 4. IL-OSC 기반 병렬 링크

그림 5. Local IL-RO 기반 병렬 링크

# 메모리 인터페이스

Differential signaling을 기반으로 한 고속 저전력 병렬 링크의 연구에 반해 메모리 인터페이스의 주류는 현재까지도 전통적인 single-ended 방식을 고수하며 세대별 회로 최적화를 통해 발전해 왔다.

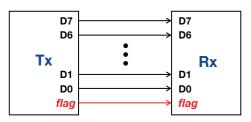

Single-ended 방식에서 신호 보전성에 치명적인 영향을 끼치는 스 바꾸면서 진화를 거듭하고 있어 반도체의 기술의 한계는 예상보다 늦 위칭 잡음의 영향을 줄이기 위해 바이트 당 한 비트를 추가하는 data bus inversion (DBI) 코딩을 적용하여 GDDR5 인터페이스에 서 최대 7Gb/s까지 발표되었다 [4], DBI 코딩은 천이하는 비트의 수 를 반 이하로 줄이는 DBI-AC [10]와 로직 0의 수를 반 이하로 줄이 는 DBI-DC [4, 5] 코딩 방법이 있는데, single-ended pseudoopen drain 출력 버퍼를 채택하고 있는 GDDR 인터페이스에서는 추가적인 전력의 감소를 얻을 수 있는 DBI-DC를 적용하고 있다.

게 아니 혹은 오지 않을지도 모른다. 결국, 끊임없이 새로운 기술이 시도되고 채택될 것이며, 여기에 맞추어 미래의 연구도 계속 새롭게 진화할 것이기 때문이다.

Flag: indicates the status of inversion.

그림 6. Data bus inversion 코딩

하지만 요구되는 데이터 전송 속도가 지속해서 증가함에 따라 기존의 single-ended 방식으로는 더 이상의 발전에 한계가 존재할 수밖에 없다. 이에 따라 차세대 메모리 인터페이스로서 3차원 구조를 이용한 병렬 링크가 활발하게 연구되고 있다. Through-silicon via (TSV) [11, 12], flip-chip 접합 [13], inductive coupling [14] 등이 그러한 것들이다. 이 중 TSV는 칩을 쌓고 물리적으로 통과시켜 연결하는 짧 은 거리에서의 병렬화를 극대화 시킨 인터페이스로서, flip-chip 접 합과 inductive coupling 방식의 단점을 모두 해결할 수 있는 기술

TSV는 저전력과 고속 통신을 동시에 실현할 수 있으면서도 회로적 으로는 저비용 single-ended signaling을 앞으로도 계속 지속할 수 있다는 만능에 가까운 해답을 제공한다고 할 수 있다. 양산을 위 해서는 웨이퍼 단계에서의 불량 칩 스크리닝에 관한 신뢰성과 패키징 후 각 층의 테스트를 효율적으로 해결할 수 있는 회로 및 알고리듬을 구비해야 하는 문제가 남아있지만, TSV가 가지고 있는 많은 장점으 로 향후 대부분의 고속 및 저전력 응용에서의 메모리 인터페이스에서 적용될 것이다.

스마트 멀티미디어 전자 기기의 급속한 발달은 병렬 링크가 고속 전 송과 저전력 소모 모두에서 한계점까지의 성능을 달성해야 함을 의미 하며, 이를 위해서는 회로, 채널, 패키징, 그리고 반도체 공정까지 가 능한 기술을 모두 포함한 새로운 도전적인 기술의 연구 개발이 요구 되고 있다. 회로의 설계적인 측면에서는 클럭 포워딩 방식을 기반으 로 다양한 직렬 링크 기술의 병렬 링크로의 효율적인 최적화가 그 해 답을 제시하고 있으며, 단일 칩 패키징을 위한 3D 구조에서는 TSV 방식이 메모리 인터페이스의 중심에서 새로운 회로 설계 및 테스트 방법에 관한 연구를 주도할 것이다.

반도체 회로 및 공정 기술의 발전은 수년 전에 한계가 될 것으로 생 각하였던 시점에 이미 와 있으나 현재도 그때와 같은 속도로 방향을

# Reference

- [1] R. Palmer, et.al., "A 14mW 6,25Gb/s transceiver in 90nm CMOS for serial chip-to-chip communications," IEEE International Solid-State Circuits Conference, pp.440-441, Feb. 2007

- [2] K. Fukuda, et.al., "A 12,3mW 12,5Gb/s complete transceiver in 65nm CMOS," IEEE International Solid-State Circuits Conference,

- [3] F. O' Mahony, et.al., "A 47x10Gb/s 1,4mW/(Gb/s) parallel interface in 45nm CMOS," IEEE International Solid-State Circuits Conference, pp.156-157, Feb. 2010

- [4] Y. Sohn, et. al., "A 7Gb/s/pin GDDR5 SDRAM with 2.5ns bank-tobank active time and no bank-group restriction," IEEE International Solid-State Circuits Conference, pp.434-435, Feb. 2010

- [5] S. Bae, et. al., "A 60nm 6Gb/s/pin GDDR5 graphics DRAM with multifaceted clocking and ISI/SSN-reduction techniques," IEEE International Solid-State Circuits Conference, pp.278-279, Feb. 2008

- [6] R. Palmer, et.al., "A 4.3GB/s mobile memory interface with powerefficient bandwidth scaling," IEEE Symposium on VLSI Circuits,

- [7] Y. Kim, et.al., "An 8GB/s quad-skew-cancelling parallel transceiver in 90nm CMOS for high-speed DRAM interface," IEEE International Solid-State Circuits Conference, pp.136-137, Feb. 2012

- [8] R. Reutemann, et.al., "A 4,5mW/Gb/s 6,4Gb/s 22+1-lane sourcesynchronous link RX core with optional cleanup PLL in 65nm CMOS," IEEE International Solid-State Circuits Conference, pp.160-161, Feb. 2010

- [9] K. Hu, et. al., "A 0.6 mW/Gb/s, 6.4-7.2 Gb/s serial link receiver using local injection-locked ring oscillator in 90nm CMOS," IEEE Journal of Solid-State Circuits, Vol. 45, No. 4, pp.899-908, Apr. 2010

- [10] M. Stan, et. al., "Bus-invert coding for low-power I/O," IEEE Transactions on VLSI Systems, Vol. 3, No. 3, pp.49-58, Jan. 1995

- [11] U. Kang, et. al., "8 Gb 3-D DDR3 DRAM using through-silicon-via technology," IEEE Journal of Solid-State Circuits, Vol. 45, No. 1,

- [12] Y. Liu, et.al., "A compact low-power 3D I/O in 45nm CMOS," IEEE International Solid-State Circuits Conference, pp.142-143, Feb. 2012 [13] US Patent 6055203, "Multi-bank architecture for a wide I/O DRAM"

- [14] N. Miura, et.al., "An 8Tb/s 1pJ/b 0.8mm2/Tb/s QDR inductivecoupling interface between 65nm CMOS GPU and 0.1µm DRAM." IEEE International Solid-State Circuits Conference, pp. 436-437, Feb.

# 타워재즈 반도체 글로벌 심포지엄 코리아

June 21, 2012 – Grand Intercontinental – Seoul, Republic of Korea

안녕하십니까.

시간의 흐름에 순응하듯 봄 꽃은 만발하고 자연의 푸르름은 절정에 다다르고 있는 멋진 봄날에 감사하며 기쁜 마음으로 인사 드립니다. 영광스럽게도 대한민국 서울에서 TowerJazz의 발전된 신 기술과 우수한 디자인 솔루션을 소개할 수 있는 두 번째 기회를 가지게 되었습

TowerJazz는 1µm~0.13µm 범위 geometry 의 Power BCD, CMOS, CIS, RF/High performance analog, SiGe process 등 특화된 Global specialty foundry leader 로 전 세계 150여 고객 이상에 Wafer를 제조 및 공급하며, 한국에서만 40여 개의 고객사를 보유하고 있는 Pure foundry manufacturer 입니다.

우수성과 탁월함을 추구한다는 목표아래 고객을 섬기는 마음으로 이 번 행사를 준비 하였사오니, 이 뜻 깊은 자리에 참석하시어 자리를 빛 내주시면 대단히 감사하겠습니다.

대상

Power management (BCD), High performance analog, CIS, RF, SiGe 반도체 관련 산업계 및 학계 인사관계자

# 그랜드 인터컨티넨탈 서울 호텔

(Grand Intercontinental Seoul Hotel)

Room: 오키드 룸 (2층)

# 찾아오시는길

# 자가용 이용

www.grandicparnas.com:444/kor/company/map/car.do

지하철 2호선 삼성역 5번 출구에서 도보로 1분

삼성역 (A): 9414, 1100, 1700, 2000, 7007, 146, 730, 341, 360, 4428, 4434,363, 143, 401, 2413, 4419, 3422, 4318

삼성역 (B): 9407, 9414, 6900, 143, 146, 401, 363, 2413, 3422, 4419, 4318, 4319, 4

# 참가방법

항래 2012 TGS 사이트에 접속 후, 페이지 하단의 참가신청서 작

- \* 한글 guide에 따라 영문으로 작성해 주시기 바랍니다.

- \* 타 Foundry 업체의 참석은 불허합니다.

# 참가신청서 URL

www.towerjazz.com/tgs/index.jsp

# 행사내용

| Time  | Subject             |

|-------|---------------------|

| 9:30  | Registration        |

| 10:00 | 개회사                 |

| 10:10 | CEO Keynote         |

| 10:40 | RF/HPA              |

| 11:30 | Non-Volatile Memory |

| 12:00 | 오찬                  |

| 13:10 | Power/Automotive    |

| 14:10 | Design Enablement   |

| 14:30 | CIS                 |

| 15:20 | 폐회사                 |

TowerJazz Korea 지사장 송영진 드림

# 타워재즈 반도체 코리아 지원팀

강소혜 (02-2635-6172, 010-7271-3012 selena.kang@towerjazz.com)

# Millimeter-Wave Phased

Array System

연세대학교 전기전자공학부

민병욱 교수

연구분야: RFIC, phased array system E-mail: bmin@yonsei.ac.kr

という。

# 서론

# Multimedia 정보 전송을 위한 Data Rate

우리 사회는 1990년대 중반 이후의 인터넷 시대를 거쳐, 이제는 유비쿼터스 멀티미디어 (ubiquitous multimedia) 시대에 들어섰다. 언제 어디서나 원하는 정보를 단순한 텍스트가 아닌 멀티미디어 동영상으로 접하고 있으며, 더 나아가 증강현실 기법을 통해 현실 세계의 공간적 제한을 넘어서려는 시도가 이루어지고 있다. 기술적인 측면에서 살펴보면, 더 많은 정보의 더 빠른 전송을 요구하는 시대이다.

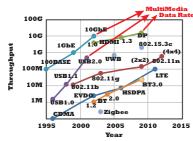

가정의 HD(high definition) TV의 정보를 압축하지 않고 실시간으로 전송하기 위해서는 3Gbps (=1920 x 1080 pixel x 24 bit/pixel x 60 frame/sec) 이상의 전송 속도를 갖는 통신이 이루어져야 한다 [그림 1].

그림 1. Multimedia 정보 전송을 위해 필요한 data rate. [1]

1990년대 중반 이후 현재까지의 통신 방식은 10년마다 거의 10배 정도로 그 전송 속도가 빨라져 왔으나, 무선 통신 전송 속도는 유선 통신 방식에 멀티미디어 통신을 위해서는 아직 많이 부족한 실정이다 [그림 2].

그림 2. 연도별 유무선 통신 방식에 따른 전송 속도

따라서 5세대 이동 통신은 이러한 멀티미디어 환경에 부합하기 위하여 최고 1천 배(x1000)의 빠른 전송 속도를 제공하는 것을 목표로 한다. 이를 위하여 10배 높은 주파수 이용 효율, 10배 많은 소형 셀기지국, 그리고 10배 넓은 주파수 대역폭을 이용하는 기술을 개발하려는 노력이 이루어지고 있다.

# 본론

# 밀리미터파 (Millimeter-Wave)

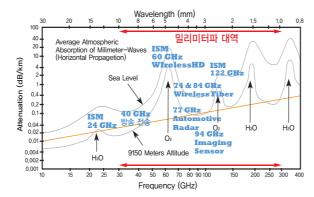

초고속 무선 통신을 구현하기 위한 주파수로 밀리미터파 대역에 관한 관심이 높아지고 있다. 밀리미터파 대역은 그 파장의 길이가 1~10mm인 30~300 GHz 초고주파 대역으로, 그동안 RF (radio frequency)에 비해 그 사용 빈도가 많이 떨어져 온 대역이다. 최근 무선 통신 기기가 늘어나면서 RF 대역의 주파수 혼잡 (frequency congestion) 문제로 넓은 주파수 대역의 확보가 가능한 밀리미터파를 이용하려는 노력이 늘어났다. 회로적인 관점에서 보면 500MHz 대역폭을 가진 회로는 RF 주파수에서 구현하기 매우 어렵지만, 밀리 미터파에서는 fractional bandwidth가 1% 정도에 불과하므로 쉽게 구현할 수 있는 장점이 있다.

전파는 주파수가 높아질수록 대기 중이나 전송선로에서 손실률이 많이 증가한다 [그림 3]. 특히 밀리미터파 대역에는 대기 중 산소나 물 분자에 의해 손실이 많이 증가하는 특정 주파수 대역이 존재한다. 따라서 밀리미터파를 이용하여 장거리 (수 km) 통신을 하는 것은 현실적으로 어려운 문제가 되지만, 최근 기지국을 늘리고 셀을 소형으로만들려는 상황에서는 큰 문제가 되지 않을 수 있다.

그림3. 밀리미터파의 대기 중 손실률과 응용 분야

주파수가 높아지면 전파가 장애물을 만나서 돌아가는 회절 (Diffraction) 현상도 약해지고 전파의 직진성이 강해진다. 따라서 밀리미터파를 이용하여 무선 통신을 하려면, 두 안테나 사이에 손실을 최소화하도록 가장 짧은 경로로 장애물이 없이 LOS(line of sight) 통신을 하도록 시스템을 꾸며야 한다. 고정 위성 통신 같은 경우에는 고지향성 안테나를 사용하여 전파 손실을 최소화하면서 LOS 통신을할 수 있지만, 이동 통신에서는 통신 위치가 계속 변화하므로 고지향성 고정 안테나를 사용할 수 없다.

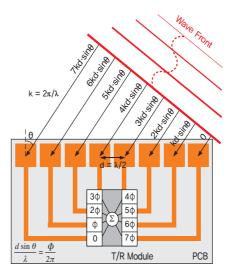

# Phased Array System

밀리미터파 이동 통신에서는 고지향성 안테나 빔을 필요한 방향으로 움직여 주는 기술이 필요하며 phased array system을 이용하면 이를 기계적이 아닌 전기적 방법으로 달성할 수 있다. 그림 4에서 보 듯이, 여러 개의 안테나로 구성된 시스템에서 인접한 안테나에 들어 오는 특정 방향의 전파 신호는 d·sinθ만큼의 경로 차이를 보이고, 전기적으로 d·sinθ/c만큼의 시간 지연 회로를 이용하여 전파 신호 를 합하면 안테나들은 원하는 방향의 전파 신호만을 수신할 수 있다.

그림 4. Phased array 안테나 개념도 (d: 안테나 간격)

실제 시간 지연 회로는 전파 대역폭이 넓지 않으면 위상 변위기 (phase shifter)로 이용하여 구현하는데,  $kd \cdot sin\theta$  (=0~360 °)만큼 의 위상 차이를 인접한 안테나에 주게 된다. 송신기도 수신기와 정확히 같은 방식으로 고지향성 빔을 조절할 수 있다.

Phased array system은 고지향성 빔을 만들고 안테나 빔의 방향을 조절할 수 있을 뿐만 아니라, 다른 여러 가지 장점이 있다. 송신기는 하나의 안테나를 사용할 때보다 각각의 안테나에서 송출되는 전력이 작아도 공간적으로 그 전력이 합쳐지는 효과가 있기 때문에, 각각의 고출력 증폭기 (power amplifier)의 출력 전력이 안테나 개수 배만큼 작아지다

수신기는 안테나의 들어온 신호는 더해질 때 같은 위상을 가지고 더해지지만, 각각의 안테나 시스템에서 발생한 잡음은 서로 다른 위상을 가지고 더해지기 때문에 신호 대 잡음비가 하나의 수신기 시스템보다 안테나 개수 배만큼 높아진다. 이러한 phased array system을 구현하기 위해서는 여러 개의 안테나에는 각각 송신과 수신을 하면서 위상을 변화시켜 줄 T/R module이 필요하다. 특히 파장이 짧은 밀리미터파 대역에서는 phased array system의 안테나의 길이와 간격 역시 짧아지기 때문에, 여러 개의 안테나를 사용하는 것이큰 부담이 되지 않는다.

# CMOS Phased Array Sy stem Architecture

공정 기술의 발달 때문에 CMOS 트랜지스터의 고속 동작이 가능해 지면서, III-V족 반도체 소자를 기판 위에서 연결하는 (Hybrid) 방식으로 설계되던 밀리미터파 phased array system을 실리콘 위에서 SoC(system on chip) 형태로 설계하려는 시도가 이루어지고 있다.

RF 소자 모델이 제공되고 있는 45nm CMOS 트랜지스터는 ft와 fmax가 각각 300GHz와 200GHz 이상이기 때문에 밀리미터파에서 동작하는 phased array system을 구현하는 것이 충분히 가능하다. 하지만 아직 밀리미터파 대역에서는 CMOS 소자 모델의 정확성이 떨어지고, 여러 기생 성분의 예측이 어려우며, 인덕터, 캐패시터, 전송 선로 등의 수동소자를 full-wave EM 시뮬레이션을 통해 설계해야 하는 어려움이 있으며 이를 극복하기 위한 시스템 구성 소자들에 대한 연구가 필요하다 [2].

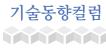

CMOS SoC 형태로 phased array system의 설계가 가능해지면 서, 여러 가지 다양한 방법의 시스템 아키텍처가 연구되고 있다 [그림 5]. 위상 변위기의 위치에 따라서 RF (밀리미터파) 위상 변위 방식과 LO 위상 변위 방식, 그리고 IF 위상 변위 방식과 디지털 위상 변위 방식이 가능하다. RF 위상 변위 방식은 한 개의 IF 회로를 가지므로 전력 손실이 가장 적고, 주파수 혼합기 이전에 안테나 빔 패턴이 만들어지기 때문에 IF 회로들의 선형성이 좋지 않아도 간섭 신호에 강한 시스템을 구현할 수 있는 큰 장점이 있다.

그림 5. Phased array system 구조 (a) RF 위상 변위, (b) IF 위상 변위, (c) LO 위상 변위와 (d) 디지털 위상 변위 방식

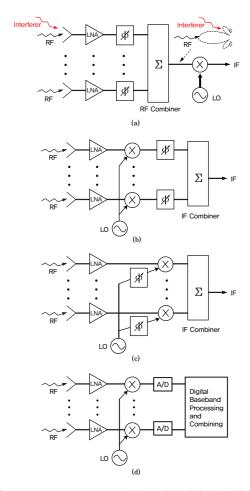

이 방식은 밀리미터파에서 CMOS 트랜지스터로 구현하기 어려운 위 상 변위기를 요구하기 때문에 LO 또는 IF 위상 변위 방식이 대안으 로 연구되어 왔다. 하지만 위상 변위기의 위상 변화 간격은 매우 세 밀할 필요가 없으므로 22.5° 위상 간격을 가지는 4-bit 위상 변위기 만을 구현하면 되고 [그림 6]. 최근의 CMOS 트랜지스터로는 100GHz에서도 충분히 4-bit 위상 변위기를 구현할 수 있다 [3].

그림 6. 4-bit 위상 변위기를 이용한 16개 안테나를 가진 phased array system의 패턴

따라서 최근에는 RF 위상 변위 방식의 phased array system이 많 이 연구되고 있다. 디지털 위상 변위 방식은 광대역 시스템을 구현하 려면, 매우 빠른 DSP (digital signal processing)을 요구하기 때문 에 전력 소모가 크며, 안테나 개수가 많이 질수록 구현이 매우 어려 워지는 문제점을 가지고 있다. [4].

# 결론

밀리미터파 phased array system 응용분야로는 40GHz의 방송 신호 전달, 60GHz WirelessHD 신호 전달, 77GHz의 차량용 충돌 방지 시스템, 74/84GHz를 이용 무선 backhaul 구현이 가능한 Wireless Fiber 기술 및 94GHz의 이미지 센서 기술들이 있다. 회로 기술의 발달에 따라 더 많은 응용분야가 생길 것으로 기대되고 있다.

# Reference

- [1] J. Laskar, S. Pinel, D. Dawn, S. Sarkar, B. Perumana and P. Sen. "the next wireless wave is a millimeter wave." microwave journal, pp. 22-36, 2007.

- [2] B. Min and G. Rebeiz, "Single-ended and differential Kaband BiCMOS phased array front-ends," IEEE Journal of Solid-State Circuits, pp. 2239?2250, 2008.

- [3] D. Kang, J. Kim, B. Min and G. Rebeiz, "Single and 4element Ka-band transmit/receive phased-array silicon RFICs with 5-bit amplitude and phase control," IEEE Transaction on Microwave Theory and Technique pp. 3534-3543, 2009.

- [4] A. Hajimiri, A. Komijani, A. Natarajan, R. Chunara, and X. Guan and H. Hashemi, "Phased array systems in silicon," IEEE communications magazine, pp. 122-130, 2004.

# Call for Papers ISOCC 2012. Theme: SoCDesign for Smart Living

# 2012 Internationa SoCDesign Conference November4-7, 2012 | Ramada Plaza Hote, Jeju, Korea

### General Chair

Kyeongsoon Cho, HUFS, Korea

# General Co-Chair

Seung Ho Hwang, Samsung Elec. Korea Jinsang Kim, Kyung Hee U. Korea Yeo Kiat Seng, NTU, Singapore

### General Vice Chair

Kwang Sub Yoon, Inha U. Korea Makoto Ikeda, U. Tokyo, Japan

# **Technical Program Chair**

Jun Rim Choi, Kyungpook Nat'l U. Korea

# Technical Program Co-Chair

Ken Choi, IIT, USA

Tony Tae Hyoung Kim, NTU, Singapore

# **Technical Program Vice Chair**

Jin-Gyun Chung, Chonbuk Nat'l U. Korea

# **Conference Secretary**

Joong-Ho Choi, U. of Seoul, Korea

# **Special Session Chair**

Hanho Lee, Inha U. Korea Chulwoo Kim, Korea U. Korea

# **Finance Chair**

Seongsoo Lee, Soongsil U. Korea Min-Kyu Song, Dongguk U. Korea Yunsik Lee, KETI, Korea

# **IEEE Liaison Chair**

Myung Hoon Sunwoo, Ajou U. Korea Yunmo Chung, Kyung Hee U. korea

# **Publication Chair**

Kwang Yeob Lee, Seokyeong U. Korea Chi Ho In, Semyung U. Korea Yong Ho Song, Hanyang U. Korea

# **Publicity Chair**

Changsik Yoo, Hanyang U. Korea Hyungtak Kim, Hongik U. Korea Nak-Woong Eum, ETRI, Korea

# **Local Arrangement Chair**

Jaeyoon Lim, Jeju Nat' I U. Korea Sang Bock Cho, U. of Ulsan, Korea

# **Poster Session Chair**

Kee-Won Kwon, Sungkyunkwan U. Korea

# **Chip Design Contest Chair**

Kwang-Hyun Baek, Chung-Ang U. Korea

International SoC Design Conference (ISOCC) aims at providing the world's premier SoC design forum for leading researchers from academia and industries. Prospective authors are invited to submit papers of their original works emphasizing contributions beyond the present state of the art. ISOCC 2012 is technically co-sponsored by IEEE CAS Society and accepted papers will be published on IEEE Xplore. We also welcome proposals on special sessions.

# **Paper Submission**

Complete 2-page to 4-page manuscript (in Standard IEEE double-column format) is requested. Papers must be submitted electronically in PDF format. Only electronic submission will be accepted. For more information, please refer to the conference website: http://www.isocc.org.

# **Areas of Interest**

Display Driver and Imaging Devices Embedded System Software Low Power Design Techniques Energy-Aware Systems Multimedia (A/V) SoCs Wireline & Wireless ICs (RF ICs) Signal Integrity/Interconnect Modeling SoC Testing and Verification

Analog and Mixed-Signal Circuits

Communication SoCs **Embedded Memories** High Speed Signal Interfaces Microprocessor and DSP Architectures SoC Design Methodology SoCs for Automotive Technology Sensor & MEMS Power Electronics (Energy Harvesting) Bio & Medical Devices

# **Special Sessions**

Proposals are solicited for special sessions. Please submit proposals for special sessions to the special session chair.

# **Chip Design Contest**

Design contest provides the academia with the opportunity to introduce their novel chip designs to the real world. The selected designs will be awarded.

# **Best Paper Awards**

The authors of selected papers will be awarded for technical contributions and their papers will be invited for publication in the Journal of Semiconductor Technology and Science (SCIE) published by Institute of Electronic Engineers of Korea (IEEK). (Visit http://www.jsts.org for submission details).

# **Important Dates**

| •Deadline for submission of special session proposal;   | Jun. 30, 2012 |

|---------------------------------------------------------|---------------|

| •Acceptance notice of special session proposal;         | Jul. 14, 2012 |

| •Deadline for submission of regular session full paper; | Jul. 21, 2012 |

| •Deadline for submission of chip design contest;        | Aug. 18, 2012 |

| •Deadline for submission of special session full paper; | Aug. 18, 2012 |

| •Notification of acceptance (all submitted papers);     | Sep. 01, 2012 |

| •Deadline for final paper submission;                   | Sep. 15, 2012 |

| •Deadline for author and early-bird registration;       | Sep. 15, 2012 |

At least one author of each accepted paper must register by September 15, 2012.

15

생산성을 고려한 설계 (Design For Manufacturability)

# 생산성을 고려한 설계

# (Design For Manufacturability)

### 서돈

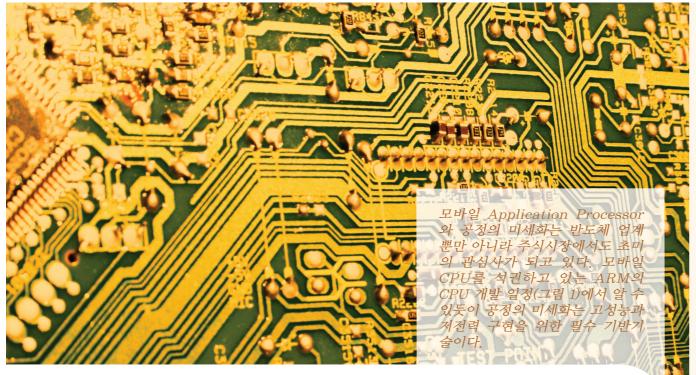

모바일 Application Processor와 공정의 미세화는 반도체 업계뿐만 아니라 주식시장에서도 초미의 관심사가 되고 있다. 모바일 CPU를 석권하고 있는 ARM의 CPU 개발 일정(그림 1)에서 알 수 있듯이 공정의 미세화는 고성능과 저전력 구현을 위한 필수 기반기술이다.

그림 1. ARM CPU Core 개발 일정

# 보로

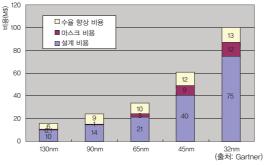

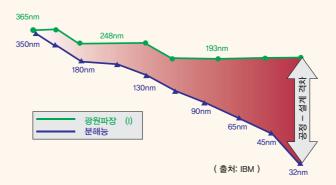

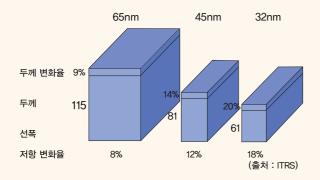

미세 공정의 발달로 같은 Die에 더 많은 회로를 구성하고 트랜지스터 내 전자의 이동거리를 줄여 집적도와 성능이 향상하고 동작전력을 줄일 수 있게 되었으나 마스크 패턴의 복잡화, 미세화로 개발기간과 비용도 큰 폭으로 증가하게되었다(그림 2). 특히 노광 (Printing) 시 광원의 파장에 비해 요구되는 마스크의 분해능 (Resolution)이 점점 높아져서 (그림 3), 설계와 실제 실리콘 간에 차이가 날 가능성이 점점 커지고 있어서, 설계 초기부터 수율 향상 (Yield Ramp-up)을 위한 노력을 기울이지 않을 수 없게 되었다.

그림 2. 공정별 제품 개발 비용

그림 3. 공정별 광원 파장과 분해능 격차

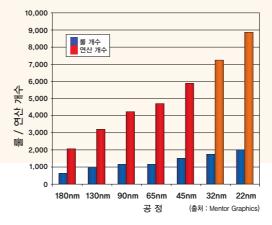

일반적으로 IC 설계와 구현이 완료되면 최종 검증단계 (Sign-off)를 거쳐 표준 마스크 설계 데이터 포맷 (GDSII: Graphic Data System II or OASIS: Open Artwork Systems Interchange Standard)으로 생산 단계로 전달되며 (Tape-out), 원하는 Mask로 제작될 수 있는지 판단하는 기하학적인 적합성을 검증한다. 해당 공정에서 허용되는 패턴의 두께와 길이, 이에 따른 적절한 간격이 기술된 설계 규칙확인 (DRC: Design Rule Check)을 통해 Mask 제작 가능 여부를 판단하게 되는데, 미세공정화에 따른 설계 규칙의 복잡도도그림 4와 같이 급격히 증가하게 되었다.

그림 4. 공정별 설계 규칙의 복잡도

특히, 광학적인 한계와 관련된 고려요인을 단순한 규칙으로 기술하기는 너무 복잡하고 어려우며 분석 단계도 일반적으로 배선이 완료된 이후에 이루어지기 때문에, 분석—〉수정—〉검증 과정이 계속 반복될 경우, 설계 일정에 상당한 부담 요인이 될 수 있다. 이러한 수율 향상을 위한 일련의 분석 및 개선과정을 설계단계부터 적용하는 것을 생산성을 고려한 설계 (DFM: Design For Manufacturability)라고 한다.

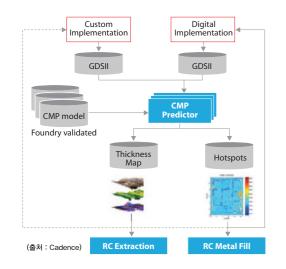

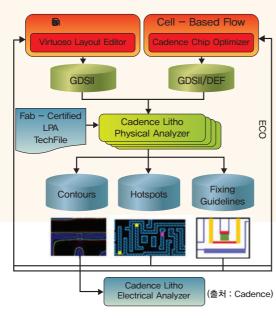

# DFM을 고려한 물리적 설계 (Layout Design)

DFM은 규칙기반(Rule-based)과 모델기반(Model-based)으로 나눌 수 있는데, 규칙 기반은 배선 (Routing) 관련 간격이나 Via 규칙 같은 DRC 관련 규칙들로 비교적 이해하기 쉽고 간단하지만 모델 기반은 리소 공정 검사 (LPC: Litho Process Check), 모조 패턴 채우기 (Dummy Metal & Via Fill), 화학적 기계적 평탄화 (CMP: Chemical Mechanical Polishing) 시뮬레이션 등다소 복잡하고 분석 시간이 길며 해결이 쉽지 않은 편이다.

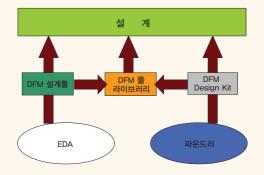

DFM은 분석 그 자체보다, 분석된 결과를 얼마나 효율적으로 반영하는가가 성 공의 관건이다. 이를 위해서는 공정의 제약 사항들이 설계자에게 잘 전달 되 고, 적용이 용이해야 한다. 그래서 무엇보다도 상용 설계 툴 설계 환경에 맞는 DDK (DFM Design Kit)가 공정 개발과 함께 준비되어 Library Release 시점에 같이 전달되어야 한다. 이를 위해선 그림 5와 같이 파운드리와 EDA (Electronic Design Automation) 업체 간의 긴밀한 협력이 필요하게 된다.

그림 5. EDA와 파운드리의 DFM 지원 모델

DFM은 설계 초기부터 적용되어야 하는데, 물리적 설계구현 (Layout Implementation) 측면에서 기판 공정 (FEOL: Front End Of the Line)과 관련해서는 주로 LPC가, 배선공정 (BEOL: Back End Of the Line)은 주로 모조 패턴 (Dummy Metal & Via) 채우기와 CMP 시뮬레이션 등이 적용된다.

이 단계에서는 다층의 배선밀도를 고르게 분포시키는데, 상세 배선 시에 민감한 신호선들 간의 간섭이 발생되지 않도록 배선경로와 배선층을 할당하고, DFM 측면에서 단락(short)이 발생하지 않게 추가적인 공간을 미리 확보해 준다.

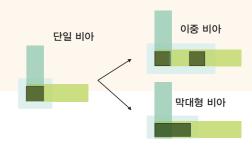

그림 6. DFM Via 최적화

# 상세 배선 (Detail Routing)

이 단계에서는 작은 구역별로 Design Rule을 고려하여 배선이 이루어지는데, DFM 측면에서 공간을 확보하거나, 신호선들의 개방(open)을 방지하기 위해 그림 6과 같이 단일 Via를 이중 Via로 교체하거나, 배선 공간 활용에 유리한 막대형 Via로 교체해준다.

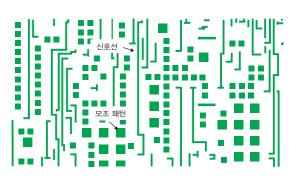

그림 7. 밀도 균일화를 위한 모조 패턴

생산성을 고려한 설계 (Design For Manufacturability)

# 모조 패턴 (Dummy Pattern) 채우기

이 단계에서는 주어진 배선층의 패턴밀도를 균일화하기 위해 그림 7과 같이 모조 패턴을 채운다. 보통 실제 신호선에 연결되지 않는 floating 상태의 패턴 이나 접지신호에 연결된 패턴을 채우게 되는데, 이 모조 패턴들에 의한 전체적인 패턴밀도의 증가로 3차원 상의 상호 캐패시턴스(Coupling Capacitance)가 증가할 수 있으므로 민감한 신호선이 있는 지역에는 충분한 공간을 확보한상태로 모조 패턴이 추가되어야 한다. 다층배선 구조상 그림 8과 같이 공정 미세화에 따라 상대적 두께 변화율이 증가하는데, 이에 따른 기생 RC (Parasitic Resistance Capacitance) 변화를 줄이기 위해 패턴의 밀도에 따른 배선층의두께 변화를 최소화해야 한다.

그림 8. 공정별 허용 두께와 저항 변화율

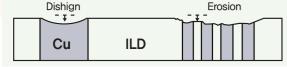

# 화학 기계적 평탄화 (CMP) 시뮬레이션

이 단계는 그림 9와 같이 평탄화 단계에서 패턴의 밀도에 따라 일어날 수 있는 배선의 과다연마(Dishing)나 배선 주변 절연체의 과다연마(Erosion) 등과 같은 문제점을 분석하고, 문제점에 대해 설계에 반영할 수 있도록 한다.

# Oxide erosion and copper dishing

(출처: IEEE Trancactions on Semiconductor Manufacturing, Vol. 18, May 2005)

그림 9. 밀도 불균일에 따른 CMP의 부작용

그림 10. 두께 변화를 고려한 RC 추출

그리고 그림 10과 같이 분석된 배선층별, 구역별 패턴 밀도를 바탕으로 예상되는 두께 변화를 고려하여, 기생 RC 추출의 정확도를 높이도록 하고 있다.

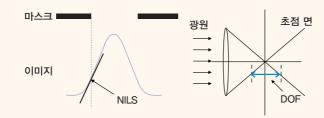

# 리소 공정 검사 (Litho Process Check)

이 단계에서는 EL (Exposure Latitude), NILS (Normalized Image Log Slope), DOF (Depth of Focus)와 같은 분해능과 관련된 고정 변수들을 바탕으로 리소 공정 시 생성될 실리콘 윤곽(Contour)을 예측하여 마스크 적합성을 분석하고 (그림 11), 그림 12와 같이 Layout에 수정 사항을 반영한다.

그림 11, NILS와 DOF

그림 12, 리소 공정 분석과 적용

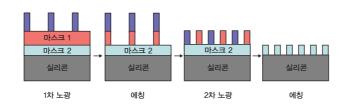

# 이중 패터닝 (Double Patterning)

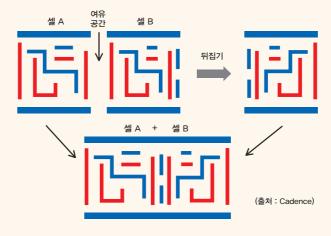

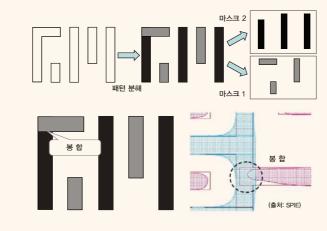

이것은 주로 20nm 이하 공정에서 적용되며 그림 13과 같이 마스크를 이중으로 만들어 분해능이 향상하는 방법으로 모든 마스크 층에 적용된다. 검증된 IP 나 셀을 배치할 때 미리 정해진 패턴 속성에 맞게 최적화하여야 하고 (그림 14), 배선 후에는 그림 15와 같이 생성된 배선 패턴에 대한 분해 (Decomposition)와 봉합(Stitching) 과정과 리소 공정 검사를 거쳐 설계상의 반영이 이루어진다.

그림 13. 이중 패터닝 리소

그림 14. 이중 패턴을 고려한 배치

그림 15. 배선 패턴의 분해와 봉합

### 결된

생산성을 고려한 설계를 주로 Layout 설계관점에서 다루었는데, DFM 규칙은 생산자(Foundry)에 의해 주도되므로 설계자 입장에서는 DFM의 효과 보다는 적용의 용이성에 더 관심을 갖게 된다.

생산자로부터 전달받은 DFM 설계 가이드를 충실히 고려한 설계 흐름(Design Flow)을 구축하여 설계 진행과 동시에 노출된 문제점들을 수정하면 원하는 수율을 얻을 수 있도록 한다. 최종 정밀 분석에서도 큰 문제점이나 수정 없이 통과해야만 진정한 의미의 DFM 환경이 구축되었다고 볼 수 있다.

DFM은 치료적 목적보다는 예방적인 성격이 강하기 때문에 파운드리-EDA 업체-설계자와의 긴밀한 협력을 통해 더욱 안정적이고 편리한 설계 환경 구축이가장 중요한 과제이다.

# LG전자 CTO SIC연구소

김명진 수석연구원

연구분야: SoC 구현 및 설계 환경 E-mail: myeongjin.kim@lge.com

# LG전자 CTO SIC연구소

백우현 연구위원

연구분야: SoC Design Technology E-mail: woohyun.paik@lge.com