# Less energy. More speed.

#### The new 30 nano class Green DDR3

Samsung's 30 nano class 46 bit DDR3 server memory chip is the most advanced, best-performing chip we've ever created. It saves 86% more energy, processes two times faster and is far more reliable than its predecessor.\*

In fact, its energy usage is so small, operating and maintenance costs of your server farm are significantly reduced. Welcome the eco-innovation that doesn't compromise performance—just one more reason the leader in green memory technology is Samsung.

www.samsung.com/greenmemory

# Newsletter

IDEC Newsletter | 통권: 제168호 발행일 | 2011년 5월 31일 발행인 | 경종민 편집인 | 김이섭 제 작 | 푸울디자인기획 | 전항기 전화 | 042) 350-8535∼6 팩스 | 042) 350-8540 http | //idec.or.kr E-mail | jhg0929@idec.kaist.ac.kr 발행처 | 한국과학기술원 반도체설계교육센터(IDEC)

Vol.168

**2011** June

IDEC NEWS | 02 디지털 신호처리를 위한 유연하고 프로그램 가능한 임베디드 디지털 프로세서 동향 | 06 용량형 센서용 Analog Front End (AFE) 설계 기술 | 12 CMOS 이미지 센서의 Dynamic Range 기술 동향 | 16

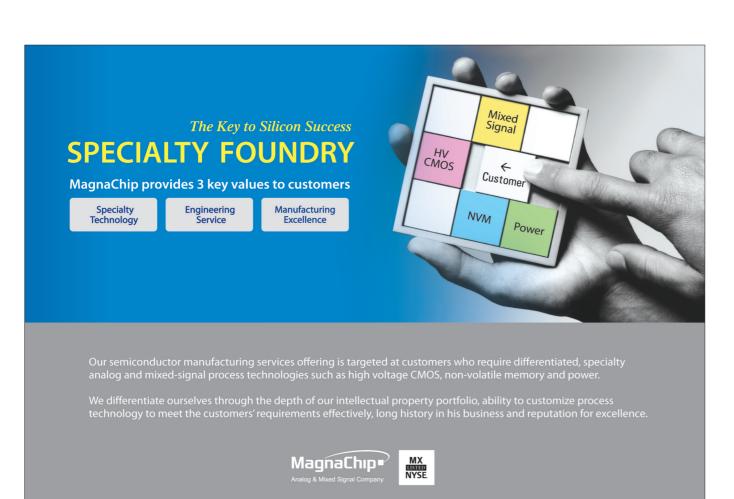

반도체설계교육센터 사업은 지식경제부, 반도체산업협회, 반도체회사(삼성전자, 하이닉스반도체, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 세미텍, TowerJazz)의 지원으로 수행되고 있습니다.

#### 디지털 신호처리를 위한 유연하고 프로그램 가능한 임베디드 디지털 프로세서 동향

디지털 신호를 이용하는 다양한 응용 분야가 지난 수십 년간 발전되어 왔고, 디지털 신호 처리를 가능하게 하는 프로세서 역시 응용분야의 다양성과 함께 진화했다. 다양한 응용 어플리케이션에서 프로그램이 가능한 솔루션은, 개발 기간의 단축, 비용의 절감을 이룰 수 있을 것으로 예상할 수 있다. 현재는 ASIC을 사용하여 이러한 디지털 신호 프로세서를 개발하는 것이 일반적인 개발방안이나, 본 고에서는 변화하는 프로세서 개발 경향에 맞추어 응용 분야에 특정된 embedded 프로세서를 유연하고 프로그램이 가능하도록 개발하는 방안을 소개한다. (관련기사 P06~11참조)

## 용량형 센서용 Analog Front End (AFE) 설계 기술

센서는 일반적으로 빛, 소리, 온도, 습도, 속도, 거리 등 측정 대상의 물리량이나 화학량의 절대치, 또는 변화량을 감지하여 유용한 전기적 신호로 변환하는 장치로 정의된다. 최근 센서 기술은 반도체 기술과 미세전기기계시스템 기술의 발전 및 시장의 폭발적 성장에 힘입어 매우 빠르게 발달하고 있다. 센서 기술은 동작 인식, 터치인터페이스 등을 가능하게 하며, 기존의 IT 기기에 새로운 기능을 부여할 수 있다는 점에서 최근 IT 분야의 핵심 기술 트렌드로 자리 잡고 있다. 본 고에서는 용량형센서의 다양한 용량-전압 변환 방식의 Analog Front End (AFE) 구조를 살펴보고, AFE 설계시의 고려 사항에 대하여 언급하고자 한다. (관련기사 P12~14참조)

### CMOS 이미지 센서의 Dynamic Range 기술 동향

CMOS Image Sensor의 응용 분야로는 휴대폰 카메라, 디지털카메라, PC 카메라, 감시 카메라, 자동차, 의료, 산업, 항공 우주 등이 있으며 그 영역은 계속 넓어지고 있다. 현재 가장 큰 CIS 응용 분야인 휴대폰 카메라용 CIS는 발전하는 CMOS 공정 기술에 기반을 두어 핵심 성능인 픽셀 소형화, 저가격화, 저전력화를 이루어 왔다. 반면 감시용, 자동차용 카메라 CIS의 경우는 운전 안정성과 감시 신뢰성을 위해 100dB 이상의 높은 dynamic range를 핵심 성능으로 요한다. 따라서 본 고에서는 향후 큰 시장 성장이 예견되는 자동차용 CIS의 필수 성능 요소인 HDR의 기술 동향을 소개한다. (관련기사 P16~19 참조)

# June | 2011 CAVS

| MPW (Multi-Project Wafer) |                                                                                                                                                              |                                                                               |              |          |                                                                            |                |                |                                             |                  |                     |                           |          |                                                                                   |                     |                |                      |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------|----------|----------------------------------------------------------------------------|----------------|----------------|---------------------------------------------|------------------|---------------------|---------------------------|----------|-----------------------------------------------------------------------------------|---------------------|----------------|----------------------|

| 신청                        | 현황                                                                                                                                                           | 1                                                                             |              |          |                                                                            |                |                |                                             |                  | 칩제작 현황              |                           |          |                                                                                   |                     |                |                      |

| 구분                        | 공정                                                                                                                                                           | 제작가능면적<br>(mm2 x 칩수)                                                          | 신청<br>팀수     | 채택<br>팀수 | 설계면적<br>(mm2 x 칩수)                                                         | DB<br>마감       | Die<br>-ou     | 비고                                          | 구분               | 공정                  | 제작가능면적<br>(mm2 x 칩수)      | 제작<br>칩수 | 제작면적<br>(mm2 x 칩수)                                                                | Die-out<br>예정일      | 현재<br>상태       | 비고                   |

| 101회<br>(11-04)           | 0.18                                                                                                                                                         | 4.5×4mm² × 20                                                                 | 21           | 20       | 4.5x4mm <sup>2</sup> x 20                                                  | 2011.<br>5.13  | 2011.<br>9.5   | DB<br>검토중                                   |                  | TJ<br>SiGe          | 5x5mm <sup>2</sup> x 1    | 3        | 5x2,5mm² x 1                                                                      | 2011.<br>5.24       | 칩제<br>작중       |                      |

| 102회<br>(11-05)           | 동부<br>BCD<br>0.35                                                                                                                                            | 5x5mm² x 3                                                                    | 10           | 6        | 5x2.5mm² x 6                                                               | 2011.<br>5.25  | 2011.<br>8.31  | DB<br>검토중                                   | 제98회<br>(11-01)  | 0.18<br>M/H         | 5x4mm <sup>2</sup> x 20   | 19       | 25x2,5mm <sup>2</sup> x 2<br>5x4mm <sup>2</sup> x 19                              | 2011.               | 칩제             | folio e I            |

| 103회                      |                                                                                                                                                              | 5x5mm <sup>2</sup> x 1                                                        | 5            | 4        | 2,5x2,5mm² x 4                                                             | 2011.<br>6.21  | 2011.<br>9.21  |                                             |                  | 0.35<br>M/H<br>0.18 | 4.5x4mm <sup>2</sup> x 20 | 20       | 4.5x4mm <sup>2</sup> x 20                                                         | 6.7<br>2011.<br>6.7 | 작중<br>칩제<br>작중 | fab out<br>: 6.1 예정  |

| (11–06)                   | 동부<br>BCD<br>0.35                                                                                                                                            | 5x5mm² x 3                                                                    | 9            | 5        | 5x5mm <sup>2</sup> x 1<br>5x2,5mm <sup>2</sup> x 4                         | 2011.<br>7.7   | 2011.<br>10.12 |                                             |                  | TJ<br>RF            | 5x5mm <sup>2</sup> x 2    | 5        | 5x5mm <sup>2</sup> x 1                                                            | 2011.               | 칩제<br>작중       | fab out              |

|                           | . ()                                                                                                                                                         | 5x5mm² x 2                                                                    | 1            | 1        | 5x5mm² x 1                                                                 | 2011.<br>8.29  | 2011.<br>11.15 | 5<br>1. 후기모집<br>20 : 5.6~<br>1.<br>20<br>2. | 제99회             | 0.18<br>동부          | 55                        | 0        | 2,5x2,5mm <sup>2</sup> x 4                                                        | 5.11                | 식당<br>PKG      | 6.16 예정<br>Die: 5.16 |

| 104회<br>(11-07)           |                                                                                                                                                              | 5x4mm² x 20                                                                   | 20           | 20       | 5x4mm² x 20                                                                | 8.29           | 12.20          |                                             | (11–02)          | BCD<br>0.35         | 5x5mm <sup>2</sup> x 3    | 6        | 5x2,5mm <sup>2</sup> x 6                                                          | 6.1                 | 제작중            | PKG : 6.7<br>예정      |

| (11 01)                   | M/H<br>0.18<br>삼성<br>65n                                                                                                                                     | 4.5x4mm <sup>2</sup> x 20<br>20개 서버<br>(4x4mm <sup>2</sup> x 48)              | 22<br>23     | 20<br>23 | $4.5 \times 4 \text{mm}^2 \times 20$<br>$4 \times 4 \text{mm}^2 \times 23$ | 2011.          | 12.20          |                                             |                  | 동부<br>0.13          | 5x5mm² x 23               | 30       | 5x5mm <sup>2</sup> x 18<br>5x2.5mm <sup>2</sup> x 8<br>2.5x2.5mm <sup>2</sup> x 4 | 2011.<br>7.6        | 칩제<br>작중       |                      |

|                           | TJ<br>CIS<br>0,18                                                                                                                                            | 5x5mm <sup>2</sup> x 1                                                        | 6            | 4        | 2,5x2,5mm² x 4                                                             | 2011.<br>10.10 | 2012.<br>1.11  |                                             | 제100회            | 동부<br>BCD           | 5x5mm <sup>2</sup> x 3    | 6        | 5x2,5mm <sup>2</sup> x 6                                                          | 2011.<br>7.12       | 칩제<br>작중       |                      |

| 105회<br>(11-08)           | 동부<br>I BCD<br>3) 0.35<br>동부<br>0.11<br>KEC 4                                                                                                                | 5x5mm² x 3                                                                    | 12           | 5        | 5x5mm <sup>2</sup> x 1<br>2,5x2,5mm <sup>2</sup> x 4                       | 2011.<br>10.13 | 2012.<br>1.18  | 설계설명 2. 회 : 5.17                            | (11-03)          | 0.35<br>삼성<br>0.13  | 4x4mm² x 48               | 37       | 4x4mm <sup>2</sup> x 35<br>4x8mm <sup>2</sup> x 2                                 | 2011.<br>8.25       | 칩제<br>작중       | DB전달<br>: 5.18       |

|                           |                                                                                                                                                              | 5x5mm <sup>2</sup> x 13<br>5x5mm <sup>2</sup> x 20<br>5x5mm <sup>2</sup> x 20 | 30<br>-<br>1 | 30 -     | 5x2,5mm <sup>2</sup> x 22<br>2,5x2,5mm <sup>2</sup> x 8<br>-<br>-          |                | 1.10<br>2012   |                                             | 제101회<br>(11-04) | TJ RF               | 5x5mm <sup>2</sup> x 2    | 8        | 2,5x2,5mm <sup>2</sup> x 5                                                        | 2011 7.19           | <sup>그</sup>   | DB전달<br>: 5.16       |

| 106회<br>(11-09)           | 삼성                                                                                                                                                           | 4x4mm <sup>2</sup> x 48                                                       | 33           | 33       | 4x4mm² x 33                                                                | 2011           | 2012           | 정규모집<br>: ~5.15<br>설계설명<br>회: 6.2           |                  |                     |                           |          |                                                                                   | 55                  |                |                      |

| 107회<br>(11-10)           | 107회 M/H (11-10) 0.18 4.5x4mm² x 20 23 23 4.5x4mm² x 2 2011 2012 정규모집 12.15 4.10 : ~6.3 ** 위의 내용은 5/27 기준임. ** 2011년 MPW 참여 일정 및 방법은 홈페이지(www.idec.or.kr) 참조 |                                                                               |              |          |                                                                            |                |                |                                             |                  |                     |                           |          |                                                                                   |                     |                |                      |

| * 107회                    | * 107회는 우선모집 결과임 전체모집 가능수의 50% 선정 * 문의 : 이의숙(042-350-4428, yslee@idec.kaist.ac.kr)                                                                           |                                                                               |              |          |                                                                            |                |                |                                             |                  |                     |                           |          |                                                                                   |                     |                |                      |

#### NDA가 체결된 Design Data 유출 금지 안내

IDEC의 MPW 참가를 통해 전달받은 Design Data 일체는 NDA를 통해서 법적인 구속력을 가지며, 관리소홀로 인한 외부로의 공개 또는 유출 시 개인뿐만 아니라 개인이 속해 있는 WG에 자격 박탈과 같은 강력한 규제가 가해질 수 있습니다. 협약에 의해, 형사상 책임을 물을 수 있음을 알려 드립니다. MPW 참여자 분들은 Design Data 및 관련 자료의 관리를 철저히 하시어 불이익을 당하는 일이 없도록 거듭 당부 드립니다.

NDA 체결 후 수령한 Design Kit 일체는 IDEC에 칩 수령 후 2개월 이내에 반드시 삭제하고, NDA 폐기확인서를 제출하여 제3자에 의한 공개 및 유출이 일어나지 않도록 주의 바랍니다.

#### **ISOCC 2011**

Thursday-Friday, November 17-18, 2011 Ramada Plaza Hotel, Jeju, Korea http://www.isocc.org

#### **2011 International SoC Design Conference**

## Call for Papers

International SoC Design Conference (ISOCC) aims at providing the world's premier SoC design forum for leading researchers from academia and industries. Prospective authors are invited to submit papers of their original works emphasizing contributions beyond the present state of the art. ISOCC 2011 is technically co-sponsored by IEEE CAS Society and accepted papers will be published on IEEE Xplore. We also welcome proposals on special sessions.

#### **Paper Submission**

Complete 2-page to 4-page manuscript (in Standard IEEE double-column format) is requested. Papers must be submitted electronically in PDF format. Only electronic submission will be accepted. For more information, please refer to the conference website: http://www.isocc.org.

#### Areas of Interest

Analog and Mixed-Signal Circuits

Display Driver and Imaging Devices

Embedded System Software

Low Power Design Techniques

Energy-Aware Systems

Multimedia (A/V) SoCs

Wireline & Wireless ICs (RF ICs)

Signal Integrity/Interconnect Modeling

SoC Testing and Verification

Communication SoCs

Embedded Memories

High Speed Signal Interfaces

Microprocessor and DSP Architectures

SoC Design Methodology

SoCs for Automotive Technology

Sensor & MEMS

Power Electronics (Energy Harvesting)

Bio & Medical devices

#### **Special Sessions**

Proposals are solicited for special sessions. Please submit proposals for special sessions to the special session chair Woo-Young Choi (<a href="wchoi@yonsei.ac.kr">wchoi@yonsei.ac.kr</a>). Chip Design Contest

Design contest provides the academia with the opportunity to introduce their novel chip designs to the real world. The selected designs will be awarded.

Best Paper Awards

The authors of selected papers will be awarded for technical contributions and their papers will be invited for publication in the Journal of Semiconductor Technology and Science (JSTS) published by Institute of Electronic Engineers of Korea (IEEK). (Visit www.jsts.org for submission details).

#### **Important Dates**

- Deadline for submission of Special Session proposal;

Acceptance potice of Special Session Proposal

- Acceptance notice of Special Session Proposal

Deadline for submission of full paper/Chip design contest;

Deadline for submission of Special Session full paper;

- Notification of acceptance (all submitted papers):

Deadline for Final Paper submission;

- Deadline for Author and Early-Bird Registration;

At least one author of each accepted paper must register by October 15, 2011.

## 2011년 IDEC Platform Center 선정

전략적 육성이 필요한 미래지향적 정보 ·

전자분야의 공동연구 수행을 통해 경쟁력을 높이기 위해서 추진하는 「IDEC Platform Center(이하 'IPC')」 사업의 2011년도 신규 센터로 광운대학교와 한양대학교가 선정 되었다.

광운대학교는 멀티미디어 기술 분야를 중점으로 한 "스마트 TV IPC", 한양대학교는 Vehicular 기술 분야의 "지능형 차량용 SoC 플랫폼 센터"로 사업을 수행할 예정이다.

선정된 두 센터는 지난 3월 사업공고 후, 1단계 서류 평가에 이어 2단계 발표 평가 및 종합심사 과정을 거쳐 최종적으로 지원이 확정되었다.

신규센터는 IT 및 융합 기술의 핵심영역에서 융복합 형 전문 플랫폼 구축을 통한 반도체 산업의 시너지 효과를 극대화하고 정부정책 및 산업체 needs에 의거한 연구센터로 운영될 것이다.

#### E<sup>2</sup>L

#### (Electrical Engineering Library)

고급 교육자료를 언제든지 다시 볼 수 있는 최적의 조건 을 이공계 학생 및 산업체 인력에게 제공할 수 있도록 교수님들의 많은 관심과 적극적인 참여를 바랍니다.

#### • 신규 교육자료 제출 방법

- 교육자료 종류 : 강의자료, 동영상 자료, 시험문제 (답안지 포함) 등

- 제출 서류 : 교육자료 등록 신청서와 교육자료

- 제출 방법 : 담당자에게 메일(sjlee@idec.kaist.ac.kr)

#### • E<sup>2</sup>L 교육자료 등록 현황

- 분야 : 반도체공학, 디지털시스템, 이날로그회로, 집적회로, 통신 & 신호처리, SoC, 초고주파회로, 컴퓨터 구조 등

- 종류 : 강의자료(PPT,PDF,HWP), 시험문제, 동영상 자료

- 자료 등록수 : 223

- \* 문의 : 이승자 (042-350-8536, sjlee@idec.kaist.ac.kr)

#### 채용 안내

• KAIST 반도체설계교육센터(IDEC)를 이끌어 갈 젊음과 열정을 가진 인재를 찾습니다.

#### 1. 모집 분야

- 모집인원 : 연구직 (신입·경력), 0명

- •자격조건 : 대졸 이상. 반도체설계 관련 전공자. 영어 능통자 우대.

- 주요업무: 국·내외 Fab을 통한 칩 설계, 제작 지원

- Digital, Analog 칩 TEST기술 지원

- EDA tool 교육 및 기술 지원

#### 2. 제출 서류

- 당사 입사지원서(홈페이지에서 다운로드)

- 최종학교 성적증명서 1부

- 졸업(예정) 증명서 1부

#### 3. 접수 기간 및 접수처

01 Aug. 2011

15 Aug. 2011

21 Aug. 2011

14 Sept. 2011

01 Oct. 2011

15 Oct. 2011

15 Oct. 2011

- 접수기간 : 2011년 6월 30일(목)

- 접 수 처 : (305-701) 대전광역시 유성구 구성동 373-1 한국과학기술원 반도체설계교육센터 104호

- 접수방법 : 우편접수, 이메일 접수

- 문 의 처 : 042-350-4045, shchoi@idec.kaist.ac.kr

- 홈페이지: www.idec.or.kr

#### 4. 기 타

- 기타 자세한 사항은 홈페이지(www.idec.or.kr) 참조

- 접수된 서류는 인비 처리하며 반환하지 않음.

IDEC Newsletter • 02 | 03

#### Core-A 교재 배포 안내

#### ▶ Core-A 교재 시리즈

|   | 교재명                            | 집필자          |

|---|--------------------------------|--------------|

| 1 | Core-A Architecture and Design | 박인철 교수       |

| 2 | Core-A 프로그래머 가이드               | 이종열 교수       |

| 3 | 반도체 배치설계 관련 지식 재산권             | 이경란 변리사 외 1인 |

| 4 | Core-A 프로세서를 활용한 플랫폼 설계        | 기안도 박사       |

| 5 | Core-A 개발보드 활용법                | 기안도 박사       |

| 6 | Core-A 프로세서 기반 System-On-Chip  | 이광엽 교수 외 공저  |

▶ 반도체설계재산 활용확산 교육 사업의 일환으로 개발된 교재를 무료로 받아 볼 수 있습니다.

#### ▶ 신청 방법

• 반도체설계재산 활용확산 사업 홈페이지(http://core-a.or.kr)에 회원 가입 후 대학지원 – 교재신청란 작성

\* 문의 : 전항기(042-350-8535, jhg0929@idec.kaist.ac.kr)

#### 대학 정규 강좌 개설 협약 안내

반도체설계재산 활용확산 교육사업의 일환으로 RISC 타입의 32bit 임베디드 프로세서인 Core-A를 이용한 정규 대학 강좌 협약을 통 해 Core-A 프로세서를 사용하는 반도체 설계 인력의 저변을 확대하고자 합니다.

#### ▶ 협약대상

• SoC 및 임베디드 시스템 설계 분야인 학과를 유치하며 Core-A 프로세서를 정규 학점제 과목으로 개설 가능한 전 국 모든 대학교

#### ▶ 협약 대학교 지원 프로그램

- Core-A를 활용한 강의 교보재 지원

- 다양한 교육 매체 서비스를 위한 교육 컨텐츠 지원

- 강의에 필요한 실습 기자재 무상 임대 지원

- 실습 기자재 활용을 위한 실습 프로젝트 예제 지원

- 반도체설계재산 활용확산 사업 홈페이지(http://corea,or,kr)에서 협약 신청서 및 강의 개설 계획서를 작성 후

- ※ 기타 자세한 사항은 홈페이지를 참조하시거나 담당자에게 문의

- \* 문의 : 김은주(042-350-8533, ejkim@idec.kaist.ac.kr)

#### 제3회 Core-A 응용경진대회

참여의향서 접수 안내

특허청과 반도체설계교육센터는 우수한 Core-A 프로세서 기반 기술을 발굴·포상함으로써 동 분야의 연구·창작의 활성화와 Core-A 프로세서를 사용하는 반도체 설계 인력의 저변 확대를 통해 Core-A 프로세서의 활용 확산을 도모 코자 Core-A 응용 경진대회를 진행한 이래, 올해로 3회째를 맞이하고 있습니다.

이에 동 경진대회에 참여를 원하시는 기업 및 기관으로부터 아래와 같이 참여 신청 및 접수를 받고 있사오니. 많은 관심과 참여를 부탁 드립니다.

#### ▶ 참여 혜택

- 동 경진대회 홍보물 제작 배포 시 참여기관 노출

- 동 경진대회 포스터 및 리플렛 등의 홍보물을 제작 해당대학 및 기업 참여기관에 발송

- IDEC 뉴스레터, 신문광고 등을 통한 홍보

- 경진대회 공식 사이트, Core-A 홈페이지, IDEC 홈페이지 등에 ▶ 신청 접수 게재

- 참여기관 광고 게재

- 작품집 : 경진대회 작품 모음집 발간에 참여기관 광고 게재

- IDEC 뉴스레터에 참여기관 광고 게재

#### ▶ 출연금액

• 100만원부터 ~ 1000만원 (참여를 희망하는 기업 및 기관으로부터 출연금을 받아 경진대회 행사 진행비 및 기탁기관 명의(특별상(기업/ 기관 브랜드))로 상금을 지급할 예정)

- ※ 특별상 시상은 진행과정 및 차후 운영위원회 회의에 의하여 변경될 수

- ▶ **참여의향서 접수** : 2011년 6월 11일(토)까지

• 반도체 설계 교육 센터 Core-A 응용 경진대회 담당자 (전화: 042-350-8533 8535 팩스: 042-350-8540)

- 후원금 출연기관에 대해서는 KAIST에서 기부금 영수증을 발급할 예정임

- 신청서는 홈페이지(http://core-a.or.kr)에서 다운로드

IDEC Newsletter • 04 | 05

## **IDEC** Distinguished Lecturer

#### About the Program

IDEC에서는 반도체 관련 분야 저명한 강사님들을 모시고 IDLP를 시작하게 되었습니다. 전국 대학, 기업체, 연구소 등 다양한 기관에서 훌륭한 초청 강연을 보다 손쉽게 접할 수 있는 기회가 되기를 희망합니다. 기술 세미나, 워크샵 등에 본 프로그램의 강사님들을 초청하시어 그 분들의 생각, 비젼, 지식을 공유하시기를 기대합니다. 더불어, 본 프로그램에 강사님으로 활동하실 분들의 적극적인 관심과 참여를 부탁드립니다.

#### Current Lecturers

A Path Towards Efficient Design and Verification of Analog /Mixed-Signal Systems

What Designers Want from Analog Circuit Optimizers :Myths and Truths Lecture 4 Equalizer Design and Performance Trade-offs in ADC-

Lecture 1 Signal Integrity Design of TSV Based 3D IC Lecture 2 Wireless Power Transfer using Magnetic Field Resonance

박영준 교수 (서울대)

Lecture 2

Understanding electrical detection of Bio molecule using

Nano MOSFET Modeling(From drift- diffusion to quantum)

(KAIST)

Lecture 1 Lecture 2

High-Performance and Low-Power ASIC Design Using Pulsed-Latches

Low-Power Low-Leakage VLSI Design: Circuits, Design Methodologies, and Best Practice Lecture 3 Heterogeneous Array of Programmable Logic: Push The

Limit of Programmable Device

강연자와 직접 연락하셔서 강연에 관한 사전 협의(날짜, 장소, 강연 내용)를 해주시기 바랍니다. 강연 관련 비용은 IDEC에서 지불하니, 강연 신청 기관에서는 지불하실 필요가 없습니다.

신청관련 및 자세한 사항은 홈페이지(http://idlp.idec.or.kr)을 참고 바랍니다. 문의: 전항기 (042-350-8535, jhg0929@idec.kaist.ac.kr)

## 디지털 신호처리를 위한 유연하고 프로그램 가능한 임베디드 디지털 프로세서 동향

(A Survey on building flexible and programmable embedded digital processor for digital signal processing)

DMC연구소 모뎀팀

이용준 박사

연구분야: SoC내 프로세서 아키텍쳐 연구 및 응용 E-mail: yj324.lee@samsung.com

DMC연구소 Media SOC팀

김경호 상무

연구분야: 카메라/휴대폰/DTV향 Media Processing SOC 개발 및 Connectivity기술

E-mail: kyungkim@samsung.com

#### 요약

디지털 신호를 이용하는 다양한 응용 분야가 지난 수십 년간 발전 되어 왔고. 디지털 신호 처리를 가능하게 하는 프로세서 역시 응용 분야의 다양성과 함께 진화하여 왔다. 이러한 디지털 신호처리 프로 세서가 사용되는 대표적인 응용분야의 예로써 DTV(Digital Television), Digital Radio, Wireless Handset 등이 있다. 다양한 응용 어플리케이션에서 프로그램이 가능한 솔루션은, 개발 기간의 단축, 비용의 절감을 이룰 수 있을 것으로 예상할 수 있다. 또한 이러한 프로그램 가능하며 유연성이 있는 개발은 시장이 필요한 적기에 제품을 공급하고, 변하는 표준에 맞추어 성능을 향상 시키고, 유지 비용을 줄이는 것이 가능하게 된다.

현재는 ASIC (Application Specific Integrated Circuit) 을 사용 하여 이러한 디지털 신호 프로세서를 개발하는 것이 일반적인 개발 방안이나, 본 소개에서는 변화하는 프로세서 개발 경향에 맞추어 응용 분야에 특정되어 있는 embedded 프로세서를 유연하고 프로 그램이 가능하도록 개발하는 방안에 관하여 소개한다. Embedded 디지털 신호 프로세서는 하나의 IC (Integrated Circuit) Chip 에 축약될 수 있는 시스템을 의미한다. 이러한 프로세서를 개발하는 다양한 방안이 있으나, 계속하여 증가하는 개발 비용과 개발된 프로 세서를 다양한 기준에 적용하기 위하여 유연한 개발방안에 관한 연구가 진행되고 있으며 이에 관한 최근의 개발 동향에 관하여 아래 에 검토하였다.

#### 신호 처리 프로세서의 개요

#### Architectural consideration

일반적인 ASIC 디자인 방식은 디지털 신호 처리의 단계를 중요한 기능 별로 분석 및 분해 하는 것이 처음 단계이다. 각 부분은 처리 비율 (Processing Rate), 입력 클락(Input Clock), 메모리 용량 (Memory Requirement), 그리고 데이터 처리 용량(Data Throughput)에 따라서 결정된다. 이러한 분석에 기반하여 RTL(Register Transfer Level) 을 설계하고 전력, 성능, 면적 등을 고려하여 설계를 수행 하게 된다. ASIC 설계 및 수행은 정확하게 필요한 요구에 맞게 설계 하여 제작할 수 있는 장점이 있으나. 유연성의 관점에서 두 종류의 큰 단점을 가지고 있다.

제 일의 단점은 많은 시간과 노력이 효율적인 하드웨어 블록을 재 사용하는 것에 필요하게 되며, 서로 다른 복수의 동작을 위하여서는

각기 다른 설계 및 개발이 필요하게 되고 이는 비용과 시간 면에서 단점이 된다. 다음으로 표준이 변경되는 경우 새로운 표준을 기존 디자인에서는 구현하는 것이 불가능하므로 새로운 ASIC 을 설계 하여 구현 해야 한다.

이러한 ASIC 을 이용한 설계와 구현의 단점들은 특정 목적의 신호 처리 프로세서를 사용하여 보완이 가능하다. 이러한 신호처리 프로 세서는 유연성과 프로그래밍이 가능한 장점이 있다. 유연성의 정도는 신호처리 프로세서를 사용하는 목적과 비용, 기간 등에 따라 결정될 수 있을 것이다.

일반적인 범용 프로세서를 사용하는 것은 가장 높은 수준의 유연성 과 프로그래밍에 의한 기능 구현이 가능하나, 전력, 성능, 그리고 칩 크기에 제한을 받는 동적 기기에 사용되는 칩을 개발 구현하는 방안으로 적합하지 않다. 지난 10년 동안 이러한 특정 신호처리를 위 한 다양한 시도들이 상용, 연구 분야에서 이루어져 왔으며, 이러한 분야의 진보 역시 다른 디지털 분야와 같이 획기적으로 발전되어 왔다

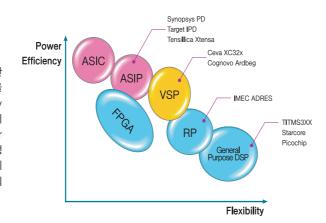

아래의 그림은 다양한 특정 신호처리를 위한 프로세서들을 유연성과 전력 효율을 고려하여 도식화 한 다이아 그램이다. 신호처리 프로 세서의 전력 효율은 ASIC 에 도달하였다고 말할 수 없다. 그러나 ASIC으로 개발 및 구현하는 것에 비하여 프로세서 개발방식은 기간 및 소요 인원에서 많은 단축을 가져올 수 있다.

그림 1. 유연성과 성능에 관한 비교 다이아그램

## 유연성과 프로그램 가능한 신호 처리 기술

FPGA (Field Programmable Gate Array) 는 개발을 검증하는 곳에서 디지털 신호처리를 변경할 수 있도록 고안된 개발방안이다. 일반적으로 FPGA는 2차원의 일반 목적 신호처리 서킷 (General-Purpose Logic Circuits) 으로 구성 되어 있으며, 프로그래밍 가능한 설계로, 이를 셀 (Cell) 혹은 블록 (Logic Block) 이라고 한다. 각 블록은 프로그래밍이 가능한 버스 (Bus) 로 연결되어 있다. FPGA 는 프로그래밍이 가능한 상호연결 (Interconnect Routing) 구조로 제한이 없는 신호처리 모듈 (Logic Module)을 선택적으로 연결 하여 신호처리 모듈의 기능을 검증한다.

기본적인 FPGA 는 구성변경이 가능한 신호처리 블록 (CLB: Configurable Logic Block) 과 입력 출력 블록 (IOB: In/Out Block)으로 구성되어 있다. 입력 출력 블록은 칩 외부에서 신호를 받아들이고 선택적으로 상호연결 블록을 구동하여 동작하게 한다. FPGA 는 수십만 혹은 수백만 신호처리 소자 (Gate Logic)를 수십 MHz의 속도로 동작하는 것을 지원한다. FPGA 는 프로그래밍 데이터 를 신호처리 블록, 상호연결 구조에서 접근이 가능한 메모리 셀에 로딩하여 프로그램 할 수 있다. 이러한 FPGA 기술은 각종 응용분야 의 개발에 유연하고 프로그램 가능한 방안으로 널리 사용되고 있다.

#### ■ Vector Signal Processor(벡터 신호 처리 프로세서)

#### ▶ 벡터 신호 처리 프로세서 소개

VSP (Vector Signal Processor) 는 DSP (Digital Signal Processor) 가 도달할 수 없는 고성능의 계산이 필요한 분야에 사용하기 위하여 개발되었다. VSP 는 DSP 를 사용하는 경우 많은 시간과 자원을 사용할 수 밖에 없는 경우에 VSP 를 사용하여 획기적 으로 성능을 향상한다. 예를 들어 Vector 계산에 DSP 를 사용하는 경우 Vector 의 크기가 증가하는 경우 시간과 프로세서의 자원이 많이 사용되나 VSP 의 경우는 넓은 프로세서의 계산 단위에 의하여 짧은 시간에 효율적으로 프로세서를 사용할 수 있다. 이 경우는 이를 VSP 라는 용어를 사용하여 DSP 와 구별하는 것이 필요하다. 높은 계산 능력에 도달하기 위하여 DSP 를 다양한 방법으로 복잡화 그리고 집적화를 실시하여 왔다 아래의 방법들이 일반적인 성능 향상 방안

• Super Pipelining Architecture (고성능 파이프 라인 구조): 수학적 계산 단위들을 연속하여 연결 하여 구조를 구성한다. 이는 연속적인 계산에 있어서 높은 효율을 제공할 수 있다.

- Super Scalar Architecture (고성능 다층 연산 구조): 여러 개의 짧은 파이프 라인을 병렬로 연결하여 사용한다. ILP (Instruction Level Parallelism) 의 방식으로 프로그램을 수행 하므로, SMP (Symmetric Multi Processing), SMT (Symmetric Multi Threading) 의 방식으로 프로그램을 구성 하 며, 많은 계산 자원이 필요하게 된다.

- Multi-DSP (다중 DSP): 다중의 프로세서들을 연결하여 사용 하는 방식이다. 다중 DSP 방식은 일반적으로 저 전력 상용화 제품이 상용되는 시장에는 적절하지 않다.

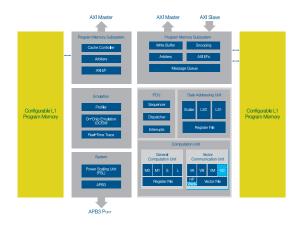

VSP의 구조는 SIMD (Single Instruction Multiple Data: 단일 명령어 다중 데이터)와 MIMD (Multiple Instruction Multiple Data: 다중 명령어 다중 데이터) 구조의 결합 프로세서이다. SIMD 구조에서는 일반적으로 LIW (Long Instruction Word)의 명령어와 결합하여 단일 명령어에 여러 가지 데이터를 처리하기 위한 기능 블록을 구동할 수 있게 사용한다. MIMD 는 각 기능 블록들이 서로 다른 처리시간과 동기만남을 지원하는 경우 처리하기 위한 프로세서 구조이다. VSP 는 앞으로 발전이 예상되는 유연하고 프로그램이 가능한 신호처리 프로세서에 사용하기 위하여 DSP 에서 진화한 것이다. 이러한 VSP 에 적합한 두 프로세서를 소개한다.

#### Ardbeg

Ardbeg VSP는 미국 미시간 공과대학과의 SODA 프로젝트에서 이루어진 연구를 바탕으로 ARM사가 상용화를 위하여 새로이 설계한 프로세서 기술이다. 이 기술은 현재 무선 모뎀을 위하여 시작되었 으나, 앞으로는 다중 미디어, 혹은 차세대 게임 콘솔, 복잡 이미지 처리 등으로 확장이 가능할 것이다. 이는 미래세대에 있어서 더 많은 계산량과 벡터화 된 응용 분야의 증가는 피할 수 없을 것으로 예상이 되기 때문이다.

SODA 연구는 SDR(S/W defined Radio)에 관한 연구로 SDR 의 장점을 구현할 수 있는 VSP를 개발하는 데 중점이 있다. SDR 이 일반 ASIC 에 기반한 Embedded 프로세서에 비하면 몇 가지 장점이 있다. 1)복수의 프로토콜을 동일한 하드웨어를 사용하여 지원 한다. 2)소프트웨어에 대한 검증의 노력이 적다. 3)동일한 하드웨어 를 복수의 프로토콜이 공유하므로 개발비용이 절감될 수 있다. 4) 미래의 프로토콜 변화에 쉽게 대응할 수 있다.

이러한 장점에 대응하기 위하여 GP-DSP 를 사용하는 경우 처리 능력의 제한으로 사용하기에 적절하지 않다. 이러한 이유로 SODA는 높은 계산 량과 유연성을 동시에 만족하기 위하여 개발되었고.

Ardbeg 은 무선 통신들, 혹은 여러 다양한 DLP(Data Level Parallelism: 데이터 구분 병렬처리) 처리에 유리하게 성능이 향상되었다.

이러한 SODA 그리고 Ardbeg에서 에너지(energy) 와 처리시간 (Delay) 그리고 칩 면적(Area) 에 바탕을 둔 최적의 SIMD 크기가 존재한다는 것이 연구 되었다. 이에 따르면 SIMD의 기능 처리 블록의 크기가 16-32 인 경우 에너지, 처리시간, 그리고 칩 면적을 고려한 최적의 구조가 된다. 실제 상용화 되는 과정에서 필요한 사항들은 아래와 같은 것들이 있다.

- SIMD/SIMD LIW 필요: 이는 SIMD 의 필요가 1개 이상의 다중 SIMD 계산 처리기가 다양하게 존재하는 미래의 응용분야에 있어서 피할 수 없는 선택이 될 것이다.

- 데이터 처리를 위한 연산자의 크기(Data Precision)의 증가: 8/16/32-bit 등과 같이 다양한 연산자의 처리를 지원하는 것이 필요하게 될 것이다.

- 곱셈기 반응속도(Multiplier Latency): VSP 를 사용 하는 신호 처리기에 있어서 곱셈에 따른 처리시간의 감소는 피할 수 없는 선택이다.

- 레지스터(Register)의 증가: SIMD 를 고효율로 활용하기 위하여는 레지스터 파일이 응용처리를 수행하는데 충분한 수가 있어야 한다.

- 협업 프로세서 (Co-processor)의 사용: SIMD의 VSP가 높은 계산 능력이 필요한 응용 분야에 적용이 가능하더라도 어떤 특정한 하드웨어의 ASIC 블록은 프로세서에 비하여 에너지와 처리 시간 면에서 유리할 수 있다. 이러한 대표적인 블록이 Turbo-decoder 로 Ardbeg 의 경우 이를 하드웨어에서처리 하는 방안으로 수정하였다.

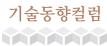

#### ▶ CEVA 사의 XC Series

CEVA 사의 VSP 구조는 기존 CEVA 사의 DSP 에서 진화하는 방식으로 진행이 되어 왔다. 아래의 그림은 XC Series 의 새로운 구성인 XC323 의 블록 구조도 이다.

그림 2: CEVA 사의 XC323 Block Diagram

일반적인 VSP 와 같이 XC 제품 군은 Vector Communication Unit(VCU: 벡터 계산기) 와 General Computation Unit(GCU: 일반 계산기) 의 두 연산 구조로 구성 되어 있다. VCU는 256-bit 의 벡터 레지스터에 의하여 동작 된다. 또한 VSP 를 사용하는 ANSI-C 처리와 조절 연산(Control Operation) 은 GCU에 의하여 동작 된다.

응용 프로그램에 있어서 통신에 기반을 한 동작과 같이 벡터로 처리가 가능한 수행 연산은 VCU에서 수행 되며, 일반적인 DSP 처리 연산과 같은 ANSI-C DSP 기능 등은 GCU 에서 인터럽트, 분지 예측 (Branch Prediction), 그리고 Delay-slot 등과 같은 Control 코드 등은 PCU(Program Control Unit) 에서 수행된다. 또한 두 개의 LSO(Load Store unit), LS1을 통하여 메모리를 접근하는 동작을 수행할 수 있도록 구성된다. 간략하게 CEVA VSP의 구성을 살펴보다면

- CEVA-XC VCU: CEVA 사는 1개의 VU(Vector Unit)에 16개 의 MAC(Multiplication and Accumulation Computation) 처리를 할 수 있도록 하고 이를 1, 2 혹은 4개를 활성화 하여 사용할 수 있도록 구조를 구성하였다. 이에 따르면 2개의 VU 를 사용하여 32 개의 16x16 bit MAC 연산이 가능하게 된다.

- CEVA-XC GCU (general computation unit): GCU는 4개 의 계산 연산자를 가지고 8/16/32/40-bit 의 계산이 가능할 수 있도록 한다. 기본적으로 Branch Control과 ANSI-C동작 수 행을 할 수 있도록 준비되어 있다.

- CEVA-XC PSU(Power Scaling Unit): CEVA-XC PSU는 여러 Clock자원에 대하여 별도의 Clock 으로 지원하는 것이 가능하다.

- CEVA-XC MSS(Memory sub system): CEVA-XC의 메모리 시스템은 데이터 메모리 시스템과 프로그램 메모리 시스템 그리고 에뮬레이션 과 디버그 시스템으로 구성 되어 있다.

#### **DSPs**

DSP(Digital Signal Processing: 디지털 신호 처리)는 수학적인 동작을 수행하는 것을 의미한다. DSP(Digital Signal Processor: 디지털 신호 처리 프로세서) 는 특별히 디지털 신호 처리의 역할을 담당하기 위하여 고안되었다. 이러한 특별한 기기들은 지난 수 10년 동안 높은 비율로 성장되어 왔고, 무선 전화 전화부터 고성능의 과학 계측 장비에 이르기 까지 다양한 용도로 사용 영역을 확대하여 왔다. 이러한 DSP를 필요에 따라서 구분을 한다면

- Application specific DSP(AS-DSP: 응용 분야 DSP), 일반적 으로 고성능의 응용분야에 적합한 성능 수요를 만족시키기 위하여 고안된 DSP 로 칩 면적과 비용을 최소한으로 한 것이다. 예를 들어 음성 변환(Speech Coding) 과 같은 예가 이에 해당한다.

- Domain specific DSP(DS-DSP: 도메인 적용 DSP), 이는 보다 광의의 응용 도메인을 담당하기 위하여 만들어진 DSP로 특정 응용 분야 적용을 염두에 두고 만들어진 DSP이다. 특별한 명령어의 추가와 추가된 H/W 를 가지고 있으며, 특정 알고리듬 (algorithm)을 효율적으로 수행할 수 있도록 최적화 되어 있다.

• General purpose DSP(GP-DSP: 범용 DSP), 이는 일반적인 응용 분야에서 사용되고 많은 기 개발의 소프트웨어를 가지고 있으나 특정 분야에 적용을 하는 점에 있어서는 다른 DSP에 비하여 성능이 낮다.

이러한 DSP의 사용은 이미 많이 알려져 왔고 널리 보편화 되어 있어 본 소개에서는 이러한 개략적인 내용만을 소개한다.

# RP(Reconfigurable Processor:(응용분야)맞춤 프로세서) RP Architecture

RP는 프로그램이 가능한 프로세서의 한 종류이다. 그러나 RP는 실제로 수행이 필요한 동작 Parameter와 데이터의 크기 및 계산의 필요에 따라서 계산 및 계산 자원 (Computing Resource)를 분배하여 적용을 하는 점에 있어서 일반 프로그램 가능 DSP 혹은 VSP 와 차이점이 있다.

실리콘 기술의 발전에 따라서 이러한 응용분야의 맞춤형의 프로세서 설계가 가능하게 되었고 이러한 프로세서 설계가 가능하도록 하는 다양한 툴들이 개발되어 왔다. 이러한 진보에 따라서 동적으로 응용 분야에 적용이 가능한 계산 능력과 성능을 보장하는 RP 프로세서 들의 개발이 급속도로 진행되고 있다. 현재의 시그널 프로세서는 계속적으로

- Data parallelism (데이터의 병렬화)

- Application-specific specialization (응용분야 특화)

- Functional flexibility (기능의 유연성)

등을 확보하는 방안으로 발전하여 왔으며 이러한 방향으로 진화하고 있다. 아래의 표는 이러한 개발방안에서 가능한 여러 방안들을 비교한 것이다. 이에 의하면 RP 는 높은 유연성과 중간 수준의 비용과 노력 그리고 ASIC 과 범용 프로세서와 중간 정도의 성능을 얻을 수 있을 것이다.

| 개발 방안           | 성능 | 개발<br>비용 | 전력<br>소모 | 유연성 |

|-----------------|----|----------|----------|-----|

| ASIC            | 높음 | 높음       | 낮음       | 낮음  |

| 프로그램<br>가능 DSP  | 중간 | 중간       | 중간       | 중간  |

| 범용 프로세서         | 낮음 | 낮음       | 중간       | 높음  |

| RP(맞춤형<br>프로세서) | 중간 | 중간       | 높음       | 높음  |

표 1. 개발 방안 별 항목 비교

이러한 RP의 일종으로 상용화가 가능한 기술로는 IMEC사의 ADRES (Architecture for Dynamically Reconfigurable Embedded Systems) 프로세서가 있다. ADRES의 프로세서 구조는 여러 기본

구조의 계산 구성요소로 이루어져 있으며 이런 계산 기본 요소는 계산기, 기억소자, 연결소자 등이다. 기본 계산 기능 유니트 (Functional Unit)는 콘트롤 신호에 의해서 동작하게 된다. 레지스터 파일과 메모리 블록들은 데이터를 저장하는 역할을 담당한다.

그림 3. ADRES 프로세서의 구성 예

연결소자는 버스와 멀티플렉서(multiplexer), 연결선(wire) 등이 있다. 이러한 연결소자를 이용하여 계산 유니트 들이 연결되어 있으며 ADRES 계산 array 를 구성하게 된다. ADRES 프로세서는 VLIW 프로세서와 세밀하게 조합이 가능한 배열 프로세서(Array Processor)로 구성되어 있다. 이러한 배열 프로세서 들은 시뮬레이터(Simulator)와 컴파일러(Compiler)를 이용하여 응용 분야에 특정된 프로세서 구조를 정하게 되고 이를 이용하여 확정된 프로세서(Processor Instance)를 만들게 된다.

ADRES 프로세서는 이러한 설계 방안에 의하여 높은 병렬화를 구현할 수 있으며, 아래와 같은 특징을 가진 맞춤형 프로세서를 얻을 수있게 한다.

- Instruction level parallelism (명령어에 따른 병렬화)

- Multi threading support (다중 쓰레드 지원)

- Vector 명령어 지원과 같은 고성능의 성능을 구현이 가능하다.

- C-프로그램에 따른 코딩

초기세대의 ADRES 프로세서는 90nm CMOS 기술에 의하여 개발 되었으며, 현재 40nm의 프로도타입 4x4 프로세서 배열(Processor Array) 모델이 개발되어 있다.

#### ■ RP 개발 방안의 예시

RP 프로세서를 이용하여 특정 응용분야에 적합한 맞춤형 프로세서를 개발하는 방안은 다음과 같다.

• XML구조 템플릿을 이용 하드웨어를 확정한다.

- 개발자는 XML을 이용 VLIW와 CGA (Coarse Grain Array) 의 크기를 정할 수 있다. 이는 FU(기능 유니트) 사이의 연결방 안에 관한 것, 데이터와 명령어 레지스터 등을 정의한다.

- 이러한 프로세서 구성 알고리듬을 기반으로 한 C-코드를 작성 하고 이를 컴파일 한다.

- 이후 ARDES 프로세서를 위한 기계어 코드가 생성된다.

- 또한 CA(Cycle Accurate) 시뮬레이션을 위한 시뮬레이터를 생성하며 통합화가 가능한 VHDL이 생성되며 이를 이용하여 ASIC 개발이 가능하다.

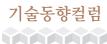

그림 4. 툴을 이용한 RP프로세서 개발 방안의 예시

## ASIP(Application Specific Instruction-Set Processor)

#### ■ ASIP 개요

ASIP은 마이크로 프로세서로 특정된 분야에 사용하기 위하여 특화된 프로세서이다. 이는 범용 성을 최소화 하여 특정 분야에서 최대한의 효율과 성능을 얻기 위한 프로세서이다. 이 프로세서는 일반프로세서와 같이 CPU, 코어, 메모리, 그리고 주변기기들로 구성된다. 가장 중요한 ASIP의 특징은 개발에 있어서 성능을 효율적으로 담보하며 짧은 개발기간과 비용의 감소가 있다.

현재의 일반적인 SoC(System On Chip)에서는 CPU와 DSP로 구별되는 2개의 프로세서를 사용하나, 앞으로는 ASIP으로 설계된다양한 프로세서 군으로 구성되는 SoC 가 진화 발전 될 것으로예상하여 이러한 ASIP 프로세서를 이용한 개발과 구현을 고려한다. ASIP은 ASIC과 범용 프로세서의 캡을 연결하는 연결고리가된다. ASIP은 범용 프로세서와 ASIC 프로세스의 넓은 영역에 걸쳐서적용이 가능하다. ASIP은 명령어 단위혹은 데이터 단위의 높은병렬화를 구현할수 있어서 일반적인 개발방안보다구조적으로특별하게구성된다. 그러므로구조적인 복잡도는 증가하게된다.

#### ■ ASIP 개발 Tool 소개

#### ▶ Target

벨기에의 Target 사는 IP Designer ASIP 툴을 제공한다. IP Designer툴은 개발자들이 ASIP구조를 정의하는 nML 언어를 이

용하여 디자인하는 프로세서를 자동적으로 생성하여 준다. nML 언어는 프로세서 디자이너가 요약하는 기본적인 정의에 맞게 다양한 형태로 프로세서를 제공할 수 있게 한다.

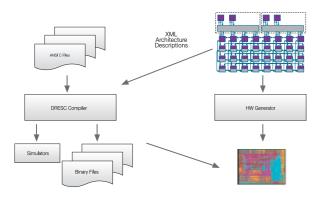

아래 그림은 IP Designer의 간단한 동작 프로세스를 나타낸다. 개발자가 정의한 프로세서 정의에 따라서 ISA 가 만들어지고, 그 러한 프로세서의 ISA 를 사용하여 개발자의 알고리듬을 컴파일, Link 하여 프로파일 후 ISA 를 수정 혹은 다음의 단계로 RTL 을 만들어 통합 RTL 을 생성하여 검증한다.

그림 5. Target사의 IP Designer 동작 환경

이러한 검증을 통과한 ASIP을 전체 SoC에 추가하여 ASIP을 사용하는 embedded 프로세서를 개발하는 것이다.

#### ▶ Tensilica

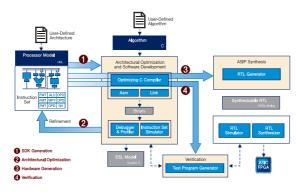

미국 소재 Tensilica사는 유사한 ASIP을 개발하는 tool 을 제공한다. 또한 Tensilica 사는 이미 기 개발된 Tensilica 사의 마이크로 프로세서를 제공하며, 이를 이용한 개발 플랫폼도 제공한다. 개발자가 개발하는 프로세서에 관한 정의의 많은 부분을 이미 메뉴 방식의 Tool 에 사용이 가능하도록 정의하였으며, 또한 특별한 ISA는 TIE(Tensilica Instruction Extension)으로 불리는 표현기능을 사용하여 새로이 정의할 수 있다.

그림 6. Tensilica사의 Xtensa 사용 ASIP 개발 Flow

상기의 그림은 Tensilica사가 제공하는 Xtensa Tool에 의하여 ASIP을 설계하고 적용하는 방안을 도식화한 것이다. 기본적으로 위에서 고려한 Target사와 유사한 방식을 사용하여 개발자는 ASIP을 개발할 수 있을 것이다.

#### 결론

앞으로도 신호 처리 기술의 영역이 줄어들 것으로 생각되지 않고 다만 확장되고 너 넓은 영역에서 사용 될 것으로 예상할 수 있다. 단 적인 예가 일본의 토요타 자동차가 클라우드 컴퓨팅을 차에서 사용하는 방안에 대하여 발표한 것이다. 이와 같이 무선 혹은 유선 신호 처리 기술의 발전은 계속될 것으로 예상이 된다. 그러나 ASIC과 같이 특정된 분야만을 위한 칩 설계 기술은 칩의 크기의 증가와 비용의 증가와 같은 기술적인 그리고 비 기술적인 요소에 의하여 제약을 받게 될 것으로 예상할 수 있다. 이러한 예상하에서 앞으로는 사용자에 특화되어 있는 ASIC 설계는 검증과 비용에 의하여 어려움에 처할 수도 있다.

이러한 관점에서 신호처리에 특화된 다양한 기술에 관하여 고찰 하였으며 이러한 기술은 곧 신호처리를 주 역할로 담당하는 embedded 프로세서에서 중요한 경향이 될 것으로 예상된다. 이에 따라서 이러한 기술을 개발하고 선점하기 위하여 이러한 기술의 이해력을 높이는 것은 필요한 것으로 생각되어 이러한 분야를 개략적 이나마 요약하였다.

## **Reference**

- http://www.actel.com/products/smartfusion/designflow.aspx

Shivi Chaturvedi, Ajay Somkuwar, "the role of digital signal processor (DSP) for 3G mobile communication systems" international journal on emerging technologies, 2010 pp23-26

- [3] TMS320C64x technical overview @ti.com

- [4] Synopsys® Processor Designer

- [5] Automating the Design and Implementation of Custom Processors and Programmable Accelerators @synopsys.com

- [6] M. Woh, et al, "From SODA to Scotch: The Evolution of a Wireless Baseband Processor," In Proceedings of MICRO'2008, pp.152 ~163

- [7] http://www.maximumpc.com/article/Intel--s-Core-is-a-Brainiac

- [8] "A NEW VECTOR PROCESSOR ARCHITECTURE FOR HIGH PERFORMANCE SIGNAL PROCESSING," Andreas Bolzer, Gerald Krottendorfer and Manfred Riener,

- [9] "Reconfigurable Computing for Digital Signal Processing: A Survey," RUSSELL TESSIER AND WAYNE BURLESON, Journal of VLSI Signal Processing 28, 7?27, 2001

- [10] http://www2.imec.be/be\_en/collaboration/ip-licensing-service /green-radio-ip-blocks.html "ADRES PROCESSOR"

# 용량형 센서용 Analog Front End

(AFE)설계 기술

충남대학교 전자공학과(Integrated Circuit Design Lab.)

연구분야 : 아날로그 집적회로, 센서 인터페이스

E-mail: hhko@cnu.ac.k

#### 머리말

센서는 일반적으로 및, 소리, 온도, 습도, 속도, 거리 등 측정 대상의물리량이나 화학량의 절대치, 또는 변화량을 감지하여 유용한 전기적신호로 변환하는 장치로 정의된다. 최근 센서 기술은 반도체 기술과미세전기기계시스템(MEMS) 기술의 발전 및 시장의 폭발적 성장에힘입어 매우 빠르게 발달하고 있다. 센서 기술은 동작 인식, 터치인터페이스 등을 가능하게 하며, 기존의 IT 기기에 새로운 기능을부여할 수 있다는 점에서 최근 IT 분야의 핵심 기술 트렌드로 자리잡고 있다.

다양한 센서 기술 중 용량형 센서는 그림 1에 도시된 바와 같이 가속도 센서, 자이로스코프, 압력 센서, 습도 센서, 정전 용량형 터치 스크린 센서 등 매우 다양한 분야에 적용되고 있다. 용량형 센서는 커패시터 의 특성상 일반적으로 온도 특성이 우수하며, DC 상태에서 전류의 흐름이 없어 저전력 구현이 가능하다는 점에서 널리 적용된다. 그러나 저항형 센서에 비하여 상대적으로 회로의 구현이 복잡하며, 기생 용량에 매우 민감하게 반응한다는 단점이 있다.

본 컬럼에서는 용량형 센서의 다양한 용량-전압 변환 방식의 Analog Front End (AFE) 구조를 살펴보고, AFE 설계시의 고려 사항에 대하여 언급하고자 한다.

touch sensing

accelerometer

gyroscope

fingerprint sensing

Humidity/ice sensor, etc...

그림 1. 용량형 센서의 다양한 응용 분야

### 용량-전압 (C-V) 변환 회로

센서의 출력 방식 중 전압 출력은 가장 널리 사용되는 방식이며, 또한 기존에 잘 알려진 아날로그/디지털 변환 기술을 이용하면 디 지털 신호로 변환이 가능하기 때문에, 다양한 용량 센싱 방식 중 용량 변화를 전압으로 변환하는 용량-전압 (C-V) 변환 회로의 구조 에 대하여 알아본다.

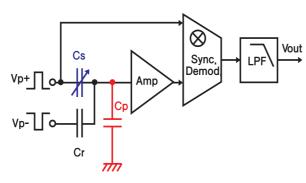

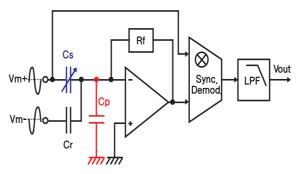

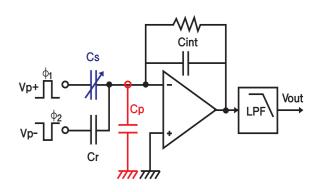

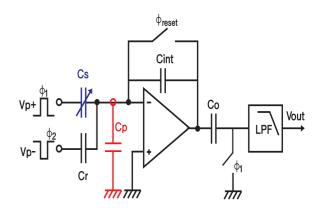

C-V 변환 회로의 구조는 크게 AC bridge와 전압 증폭기를 이용한 구조 (그림 2), transimpedance 형 증폭기를 이용한 구조 (그림 3), 연속 시간 (Continuous time, CT) chopper stabilization을 이용한 구조 (그림 4), Switched capacitor integrator와 CDS (Correlated Double Sampling)을 결합한 구조 (그림 5)의 4가지형태로 나눌 수 있다 [1-6].

그림 2의 AC bridge와 전압 증폭기를 이용한 구조의 경우, 출력 신호는 아래 식(1)과 같이 표현할 수 있다. 이때, Vp는 구동 전압, Cs는 센서 용량,  $\Delta$ C는 용량 변화, Cp는 기생 용량, Av는 전압 증폭기의 증폭도를 의미한다. 식(1)에 표현된 바와 같이, 본 구조의 경우 출력 신호가 기생 용량의 함수이므로, 기생 용량에 매우 민감 하게 반응한다. 물론, unity gain buffer를 이용한 driven shield를 이용할 경우 [2], 기생 용량에 의한 효과를 다소 감소시킬 수 있으나 증폭도가 제한되어 용량 변화가 작은 센서는 적용하기 어려운 구조 이다

$$V_{out} = V_p \frac{\Delta C}{2C_{s0} + C_p} A_v \tag{1}$$

그림 2. 전압 증폭기를 이용한 AC bridge형 C-V 변환 회로

그림 3에 도시된 transimpedance 증폭기의 경우 출력은 식(2)와 같은 형태로 표현된다. 이 경우 drive 신호는 distortion과 harmonic을 감소시키기 위하여 정현파 형태로 입력된다. 이때, fdrive는 구동주파수를 의미하며, Rf는 피드백 저항, Vm은 구동 신호의 진폭을 나타낸다. 식(2)는 구동주파수가 회로의 대역폭 내에 존재할 경우성립하며, 회로의 대역폭은 주로 f=1/(2r Rf(2Cs+Cp))로 결정된다. 큰 증폭도를 얻기 위해서는 피드백 저항을 증가시켜야 하나, 이 경우회로의 동작 대역폭이 감소하여, transimpedance 증폭기의 경우고속으로 큰 증폭도를 획득해야 하는 경우 적용이 어렵다는 단점이 있다. 그러나 회로의 virtual ground에 의해 기생 용량에 의한 효과가제거되어, 입력단과 ground 사이의 기생 용량은 회로 동작에 거의 영향을 끼치지 않는다는 장점이 있다.

$$V_{out} = 2\pi f_{drive} R_f V_m \Delta C \tag{2}$$

그림 3. Transimpedance amplifier형 C-V 변환 회로

C-V 변환기의 구조 중 가장 널리 사용되는 방식은 전하 적분기(charge integrator)를 이용하는 구조이다. 이 경우 전하 적분기의 구조에 따라 그림 4과 같이 연속 시간(continuous time, CT) chopper stabilization 구조를 이용하는 경우와 그림 5와 같이 이산 시간에서 switched capacitor(SC) CDS(correlated double sampling) 구조를 이용하는 경우로 나뉜다. 두 경우 모두 출력 전압은 피드백 저항 또는 피드백 스위치의 효과를 무시하면 식(3)과 같이 표현할수 있다.

두 방식 모두 반대 위상의 구동 신호를 이용하고 전하 증폭기를 통하여 출력을 얻기 때문에, 입력단과 접지 간의 기생 용량에 대한 변화는 대부분 상쇄할 수 있다는 장점이 있다. 1/f noise 및 offset

제거 측면에서 chopper stabilization과 CDS 방식 모두 효과적 이며 널리 사용되는 방식이나, 동일한 전력 소모를 기준으로 볼 때 chopper stabilization 방식이 더 저잡음 특성을 구현할 수 있다는 결과가 발표된 바 있다 [7].

그림 4. CT+Chopper Stabilization형 C-V 변환 회로

그림 5. SC+CDS형 C-V 변환 회로

CT 형 회로는 적분기의 안정성을 확보하기 위하여 피드백 저항을 사용하며, charge injection 및 clock feedthrough 등의 스위칭 노이즈가 없어 저잡음 구현에는 유리하다. 그러나 통상적으로 수십 MOhm 이상의 매우 큰 저항이 필요하며, 이를 구현하기 위한 많은 설계 기법들이 연구되고 있다. SC형 회로의 경우 매우 큰 저항 등 특수한 소자를 사용할 필요가 없으며, SC 회로의 특성 상 정확한

하여 신뢰성 있는 회로를 구현할 수 있다는 장점이 있다. 그러나 스위칭 노이즈로 인한 출력 잡음 특성의 열화가 SC 형 회로의 가장 큰 문제점으로 지적되고 있다. 또한, 작은 용량 변화를 감지하여야 할 경우 피드백 적분 캐패시터의 용량이 줄어들어야 하며, 이 경우 kT/C 노이즈의 증가 및 스위칭 노이즈가 더욱 증가하는 문제점이 을 전하고자 한다.

타이밍의 구현이 가능하고, 몇 개의 스위치와 캐패시터만을 이용 C-V 변환 방식 외에 많이 사용되는 용량-시간 변화, 용량-주파수 변화 등 다양한 방식의 용량형 센서에서도 기생 용량의 효과는 필수 적으로 고려되어야 할 사항이다. 본 컬럼이 용량형 센서 인터페이스 설계자들에게 조금이나마 도움이 되었으면 하는 바람을 가지며, 연재 기회를 주신 IDEC 관계자 여러분에게 지면상으로나마 감사의 말씀

$$V_{out} = V_p \frac{\Delta C}{C_{int}} \tag{3}$$

#### 용량 감지형 센서 AFE 설계의 고려 사항

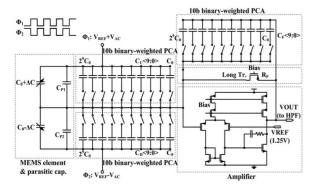

그림 6은 CT chopper stabilization 구조를 적용한 C-V 변환기 의 설계 예시이다. 실제 용량형 센서의 경우 용량 변화가 발생하는 노드와 ground 사이의 기생 용량은 대부분 virtual ground 또는 차동 증폭시 제거된다. 그러나 차동 용량 센서의 두 차동 전극 사이 에서 발생하는 기생 용량은 실제 용량 변화 신호와 구분되지 않기 때문에 기생 용량의 제거가 불가능하여. 추가적인 기생 용량 보상 회로가 반드시 필요하게 된다. 또한. 센서의 출력 산포를 제거하는 측면에서도 오프셋 및 민감도를 보상할 수 있는 회로가 추가되어 야 한다. 그림 5는 보정 기능을 갖춘 C-V 변환기의 설계 예로서, 기생 용량으로 말미암은 오프셋을 보정하기 위하여 10비트의 programmable capacitor array가 추가되었으며, 민감도 산포를 보정하기 위하여 적분기의 피드백 캐패시터도 10bit의 programmable capacitor array로 구현되었다.

그림 6. 기생 용량 및 민감도 산포 보정 기능을 갖춘 C-V 변환 회로

본 컬럼에서는 용량형 센서의 4가지 구조의 C-V 변환 방식의 Analog Front End (AFE) 구조와 특성을 살펴보고. AFE 설계시 의 고려 사항에 대하여 검토하였다. 용량형 센서의 특성상, 실제 용량 변화는 수~수백 fF 수준임에 비하여, 기생 용량은 일반적으로 수 pF 수준인 관계로, C-V 변환 방식은 반드시 기생 용량에 의한 출력 산포를 제거할 수 있는 회로 기법이 필수적으로 요구된다. 이는

### Reference

- [1] S.J. Sherman, et.al., "Low cost monolithic accelerometer", Dig. VLSI Circuits Symp., June 1992, pp. 34-35.

- [2] W. Yun, R.T. Howe, and P.R. Grav, "Surface micromachined digitally force-balanced accelerometer with integrated CMOS detection circuitry," Solid-State Sensor and Actuator Workshop, Hilton-Head Island, SC, USA, June 1992, pp. 126-131.

- [3] J. A. Geen, S. J. Sherman, J. F. Chang, S. R. Lewis, "Single chip surface micromachined integrated gyroscope with 50°/h Allan deviation, "IEEE J. of Solid-State Circuits, vol. 37, Dec. 2002, pp.1860-1866.

- [4] H. Kulah, J. Chae, N. Yazdi, K. Najafi, "A multi-step electromechanical sigma-delta converter for micro-g capacitive accelerometers," 2003 IEEE Int. Solid-State Circuits Conference, Feb. 2003, pp. 202-203.

- [5] M. Lemkin, B. Boser, "A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics. "IEEE J. of Solid-State Circuit. vol. 34. April 1999, pp. 456-468.

- [6] H. Ko, D. Cho, "Low noise accelerometer microsystem with highly configurable capacitive interface," Analog Integrated Circuits and Signal Processing, June 2011, pp. 365-373

- [7] J. Wu, G. K. Fedder, and R. Carley, "A Low-Noise Low-Offset Capacitive Sensing Amplifier for a 50 ug/rtHz Monolithic CMOS MEMS Accelerometer," IEEE J. of Solid-State Circuit, vol. 39, May 2004, pp. 722-730

반도체설계교육센터

## MPW(Multi-Project Wafer) Design Contest, 2011 IDEC MPW 설계공모전

IDEC MPW 설계공모전을 통하여 자신이 설계한 IC를 국내 최고의 Foundry 업체에서 제작할 수 있습니다 여러분이 주인공이 되어 생각을 현실로 구현해 보십시오

#### ○ 2011년 MPW 공정 지원 내역

| 공정지원사     | 공정[ɹm]                                  | 공정내역                                                                                                  | size      | 칩수 | Package                             |  |

|-----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------|----|-------------------------------------|--|

|           | 0.13µm                                  | CMOS 1-poly 6-metal                                                                                   | 4mm x 4mm | 96 | 208pin QFP                          |  |

| 삼성        |                                         | CMOS 1-poly 8-metal<br>(RF지원, Option(HRI, Inductor, MIM))                                             | 미정        | 20 | 208pin QFP                          |  |

|           |                                         | CMOS 2-poly 4-metal<br>(Optional layer (DNW, HRI, BJT, <b>CPOLY</b> ) 추가)                             |           |    | Design 144pin<br>Package 208pin QFP |  |

| 매그나칩/하이닉스 |                                         | CMOS 1-poly 6-metal<br>(6metal을 Thick metal로 <b>만</b> 사용가능<br>/Optional layer(DNW, HRI, BJT, MIM) 추가) |           | 80 | Design 200pin<br>Package 208pin QFP |  |

|           |                                         | CMOS 1-poly 8-metal<br>(RFCMOS, Top: UTM)                                                             |           | 23 | 208pin QFP                          |  |

|           |                                         | CMOS 1-poly 6-metal<br>(RFCMOS, Top: UTM)                                                             |           | 13 | 208pin QFP                          |  |

|           | 0.35 <sub>m</sub><br>BCDMOS             | CMOS 2-poly 4-metal                                                                                   |           | 15 |                                     |  |

|           | 0.18µm C <b>I</b> S                     | CMOS 1-poly 4-metal                                                                                   | 5mm x 5mm | 2  |                                     |  |

|           | 0.18μm(*)<br>BCDMOS                     | CMOS 1-poly 3-metal(MT)                                                                               |           | 2  | 지원하지 않음                             |  |

|           | 0.18µm RFCMOS                           | RFCMOS 1-poly 6-metal                                                                                 | 5mm x 5mm | 4  |                                     |  |

|           | 0.18µm SiGe SiGe BiCOMOS 1-poly 6-metal |                                                                                                       | 5mm x 5mm | 1  |                                     |  |

| KEC       | 0.5μm                                   | CMOS 1-poly 2-metal                                                                                   | 3mm x 3mm | 20 | 28pin ceramic                       |  |

|           | 4µm BJT                                 | BJT 1-poly 2-metal                                                                                    | 3mm x 3mm | 20 | 28pin ceramic                       |  |

#### ○ 2011년 MPW 진행 일정

|                             | 공정사           | 공 정                  | 제작칩수 | 우선모집     |          | 정규모집     |          | 후기              | DB마감       | DB전달     |          | Package  |

|-----------------------------|---------------|----------------------|------|----------|----------|----------|----------|-----------------|------------|----------|----------|----------|

| 구 분                         |               |                      |      | 신청마감     | 선정발표     | 신청마감     | 선정발표     | 접수시작<br>(선확순마감) | (Tape-Out) | (Fab-In) | Chip-out | -out     |

|                             | TowerJazz     | 0.18µm (SiGe)        | 1    |          |          | 10.10.31 | 10.11.15 |                 | 11,02,11   | 11.02.22 | 11.05.24 | 11.06.24 |

| 98회<br>(11-1)               | 매그나칩/<br>하이닉스 |                      |      |          |          | 10,10,31 | 10,11,15 |                 |            |          | 11,06,07 |          |

|                             | 매그나칩/<br>하이닉스 | 0.18µm               |      |          |          | 10.10.31 | 10.11.15 |                 | 11.02.11   | 11.02.25 | 11.06.07 |          |

|                             | TowerJazz     | 0.18µm(RF)           |      |          |          | 10,11,20 | 10,12,06 |                 | 11,02,21   | 11.03.07 | 11,05,11 |          |

| 99회                         | 동부            | 0,35μm<br>(BCDMOS)   | 3    |          |          | 10,11,20 | 10,12,06 |                 | 11.02.22   | 11.03.09 | 11,06,01 | 11.07.01 |

|                             | 동부            | 0,13µm               |      |          |          | 10,11,20 | 10,12,06 |                 | 11,03,21   | 11.04.06 | 11,07,06 | 11,08,06 |

| 100회                        | 동부            | 0,35 µm<br>(BCDMOS)  | 3    |          |          | 10,12,05 | 10,12,20 |                 | 11.04.07   | 11,04,20 | 11,07,12 | 11,08,12 |

|                             | 삼성            | 0.13µm               | 48   |          |          | 10.12.05 | 10.12.20 |                 | 11.04.25   | 11,05,09 | 11,08,25 | 11.09.10 |

|                             | TowerJazz     | 0,18µm(RF)           | 2    |          |          | 10.12.15 | 10.12.30 | 11,02,01        | 11.05.02   | 11.05.16 | 11.07.19 | -        |

| (11–4)                      | 매그나칩/<br>하이닉스 | O.18µm               |      |          |          | 10.12.15 | 10.12.30 | 11.02.01        | 11.05.13   | 11.05.27 | 11.09.05 |          |

| 102회<br>(11 <b>-</b> 5)     | 동부            | 0.35 µm<br>(BCDMOS)  |      |          |          | 11.01.05 | 11,01,20 | 11.03.15        | 11.05.25   | 11.06.08 | 11.08.31 | 11,09,30 |

|                             | TowerJazz     | 0.18µm(CIS)          | 1    | 10,12,05 | 10,12,20 | 11.02.06 | 11.02.20 | 11.04.06        | 11,06,21   | 11.07.05 | 11.09.21 | -        |

| (11–6)                      | 동부            | 0,35µm<br>(BCDMOS)   |      |          |          | 11.02.06 | 11,02,20 | 11.04.06        | 11,07,07   | 11.07.20 | 11,10,12 |          |

|                             | TowerJazz     | 0.18µm<br>(BCDMOS)   |      |          |          | 11.03.02 | 11.03.15 | 11.05.06        | 11.08.29   | 11.09.14 | 11.11.15 |          |

|                             | 매그나칩/<br>하이닉스 | 0.35μm               | 20   |          |          | 11.03.02 | 11.03.15 | 11.05.06        | 11.08.29   | 11.09.14 | 11.12.20 |          |

|                             | 매그나칩/<br>하이닉스 | 0.18µm               | 20   |          |          | 11.03.02 | 11.03.15 | 11.05.06        | 11.08.29   | 11.09.14 | 11.12.20 | 12.01.20 |

|                             | 삼성            | 65nm                 | 20   |          |          | 11,03,02 | 11,03,15 | 11,05,06        | 11,08,19   | 11,09,05 | 12,01,15 | 12,02,15 |

|                             | TowerJazz     | 0.18µm(C <b>I</b> S) |      |          |          | 11.04.15 | 11.04.29 | 11,07,15        | 11,10,10   | 11,10,24 | 12,01,11 |          |

|                             | 동부            | 0.11µm               |      |          |          | 11.04.15 | 11.04.29 | 11.07.15        | 11,10,10   | 11,10,26 | 12,01,10 |          |

| 105회<br>(11 <del>-</del> 8) | 동부            | 0.35µm<br>(BCDMOS)   |      |          | 11.02.08 | 11.04.15 | 11.04.29 | 11,07,15        | 11,10,13   | 11,10,26 | 12,01,18 | 12,02,18 |

|                             | KEC           | 4μm                  | 20   | 11.01.20 |          | 11.04.15 | 11.04.29 | 11,07,15        | 11,10,14   | 11,10,28 | 12,01,27 | 12,02,27 |

|                             | KEC           | 0 <u>.</u> 5µm       | 20   |          |          | 11.04.15 | 11.04.29 | 11.07.15        | 11,10,14   | 11,10,28 | 12.01.27 | 12,02,27 |

| 106회<br>(11 <del>-</del> 9) |               | 0,13µm               |      |          |          | 11,05,15 | 11,05,30 | 11,08,15        | 11.11.05   | 11,11,25 | 12,03,09 |          |

| 107회<br>(11-10)             | 매그나칩/<br>하이닉스 | 0,18µm               | 20   |          |          | 11,06,30 | 11,07,15 | 11,08,31        | 11,12,15   | 11,12,30 | 12,04,10 | 12,05,10 |

#### 참여 대상: IDEC Working Group(WG) 대학의 학부생 및 대학원생

- 우선모집 / 정규모집의 참가신청팀은 50:50으

후기모집은 정규모집 미달시에만 실

# CMOS 이미지 센서의 Dynamic Range 기술동향

연구분야: Nano-Quantum IC, CMOS image sensor, Single photon detector & OEIC

E-mail: khyang@ee,kaist.ac.kr http://hsnl.kaist.ac.kr

KAIST 전기 및 전자 공학과

백인규

연구분야: CMOS image sensor E-mail: ikbaek@kaist.ac.kr

#### 서론

CMOS Image Sensor(CIS)는 1967년도에 처음 발명되었지만, Passive-type Pixel(픽셀) 구조의 한계로 당시 Charge Coupled Device(CCD) 대비 낮은 동작 범위(dynamic range), 높은 잡음 등으로 말미암아 화질이 열등하여 이미지 시장에서 부각되지 못했다.

이 후 CIS는 CMOS Active-type Pixel Sensor (APS)의 개발, CMOS 공정 기술의 발전, 신호 처리 방법 개선 등으로 인해 1990년대 후반부터 기존 CIS 화질의 문제점을 개선한 연구가 광범위하게 발표 되면서 CCD의 경쟁 상대로 다시 부각하게 되었다. 현재 CIS는 개선 된 화질과 더불어 CCD 대비 저전력 소모, 저가 공정, CMOS 회로 집적을 통한 시스템 단일칩화 등의 지속적인 특성 향상에 의해 CCD보다 큰 시장 경쟁력을 확보하고 있다[1].

CIS의 응용 분야로는 휴대폰 카메라, 디지털카메라, PC 카메라, 감시 카메라, 자동차, 의료, 산업, 항공 우주 등이 있으며 그 영역 은 계속 넓어지고 있다. CIS의 중요 성능 요소로는 dynamic range, 잡음, 동작 속도(frame rate), 민감도(sensitivity), 화소 (resolution), 색 표현, 소비 전력, 센서 크기 등이 있으며, 그 응용 분야에 따라 각기 다른 성능을 필요로 한다.

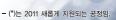

현재 가장 큰 CIS 응용 분야인 휴대폰 카메라용 CIS는 발전하는 CMOS 공정 기술에 기반을 두어 핵심 성능인 픽셀 소형화, 저가격 화, 저전력화를 이루어 왔다. 반면 감시용, 자동차용 카메라 CIS의 경우는 운전 안정성과 감시 신뢰성을 위해 100dB 이상의 높은 dynamic range를 핵심 성능으로 요한다. 따라서 본 컬럼에서는 향후 큰 시장 성장이 예견되는 자동차용 CIS의 필수 성능 요소인 high dynamic range(HDR)의 기술 동향을 소개한다.

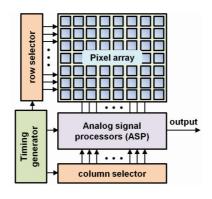

#### ■ CIS 시스템 및 픽셀 구조

다음 그림 1은 CIS 시스템의 구성을 나타낸 것이다. CIS는 수광에 의해 생성된 전하를 전압으로 변화시키는 2차원 픽셀 배열, 픽셀의 access를 위한 행(row)과 열(column)의 선택 회로, 수광에 의해서 발생한 각 픽셀의 출력 전압을 잡음 제거 등의 간단한 신호 처리 후 디지털 신호로 변환하는 아날로그 신호 처리(ASP) 부분으로 구성

그림 1. CIS 시스템 구성

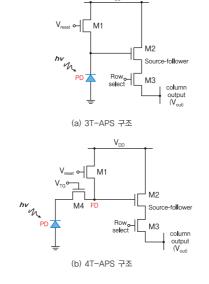

여기서 2차원 픽셀 배열을 이루고 있는 active pixel sensor (APS)는 픽셀을 이루는 트랜지스터의 수에 따라 대표적으로 3T-APS 구조와 4T-APS 구조로 나뉜다. 다음 그림 2(a)는 포토다이 오드를(PD) 이용한 일반적인 3T-APS 구조이며, 그림 2(b)는 pinned photodiode(PPD)를 이용한 일반적인 4T-APS 구조이다.

그림 2. 3T-APS 구조와 4T-APS 구조

현재 산업화된 대부분의 CIS 제품은 pinned photodiode(PPD)를 이용한 4T-APS 구조를 사용한다. 이는 4T-APS 구조가 3T-APS 구조 대비 낮은 잡음과 픽셀 소형화의 장점이 있기 때문이다.

#### ■ Dynamic range 정의 및 특징

Dynamic range란 이미지 센서가 감지 가능한 빛 세기의 범위를 나타낸 것으로, 이는 다음 식(1)과 같이 나타낼 수 있다. 즉, dynamic range 값이 크면 촬영 대상에 밝은 빛과 어두운 빛이 같 이 있더라도 이를 차별하여 하나의 이미지에 구현할 수 있다.

Dynamic range(dB)=

$$20 \cdot \log(\frac{\text{saturation signal}}{\text{rms noise floor}})$$

따라서 높은 dynamic range를 구현하기 위해서는 낮은 잡음 특성과 높은 포화 신호 크기를 가져야 한다. 신호의 크기가 잡음의 표준 편차 이하라면 신호는 잡음에 묻혀서 감지가 안되므로, 만약 잡음이 감소하면 약한 빛으로의 감지 가능한 빛 범위가 확장되어 dynamic range가 커지게 된다. CIS에서의 잡음은 shot 잡음, 열(kTC) 잡음, 회로 잡음, 고정 패턴 잡음(fixed pattern noise, FPN)이 있다. 여기서 고정 패턴 잡음은 offset FPN과 gain FPN으로 나뉜다. 암전류(dark current)에 의한 offset FPN과 열잡음은 CIS에서 일반적으로 사용되는 correlated double sampling(CDS) 회로를 통해 제거가 가능하며 약한 빛에서 gain FPN은 shot 잡음에 비해서 무시되므로, dynamic range를 크게 하기 위해서는 암전류 shot 잡음과 회로 잡음의 감소가 필요하다.

하지만 잡음 특성이 3T 대비 상대적으로 우수한 4T-APS의 dynamic range가 50~60dB인 점을 감안하면, 회로 잡음의 감소만으로는 100dB 이상의 HDR을 구현하기는 어렵다. 또한, 발달하는 CMOS 공정 기술과 함께 낮아지는 센서의 동작 전압과 floating diffusion (FD) 구조에 따른 전체 well capacity의 한계로 말미암아 포화 신호 크기가 제한되어 강한 빛으로의 감지 가능한 빛 범위 확장 역시 어렵다. 따라서 일반적인 동작을 가진 4T-APS의 자체 성능만으로는 100dB 이상의 높은 dynamic range를 요하는 감시용, 자동차용 카메라로의 응용이 어렵기 때문에 픽셀 및 주변 회로의 변화를 통한 dynamic range의 확장이 필요하다.

#### ■ High dynamic range 기술 소개

픽셀 및 동작 방법의 변화를 통한 대표적인 high dynamic range (HDR) 구현 기술은 다음의 표 1과 같다.

| 응답 종류                      | HDR 구현 기술                                                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Non-linear<br>Response HDR | · Logarithmic [2, 3]<br>· Logarithmic with a low FPN [3, 5]<br>· Linear-logarithmic [4]                                     |

| Reoponee HBR               | · Well-capacity adjustment [6]                                                                                              |

|                            | · Dual sensitivity [7, 8]                                                                                                   |

| Linear Response HDR        | <ul> <li>Dual sampling [9]</li> <li>Dual sampling without line memories [10, 11]</li> <li>Multiple sampling [12]</li> </ul> |

|                            | · Saturation detection [13]                                                                                                 |

|                            | <ul> <li>Lateral overflow integration<br/>capacitor (LOIF) [14]</li> </ul>                                                  |

|                            |                                                                                                                             |

표 1. 대표적인 high dynamic range 구현 기술

#### ■ Non-linear 응답의 HDR 기술

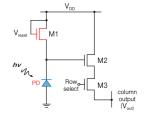

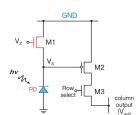

Non-linear 응답의 가장 대표적인 HDR 기술은 logarithmic 특성 이 있는 로그 센서이다. 로그 센서는 전류-전압 간의 logarithmic 특성 관계를 이용하며, 대표적으로 MOS 트랜지스터의 subthreshold 특성 및 다이오드의 순방향 전류-전압(photovoltaic) 특성을 이용하여 구현된다. 그림 3은 각각의 로그 센서의 구조를 나타낸다[2, 3].

(a) Sub-threshold 특성 기반의 로그 픽셀[2]

(b) 다이오드 순방향 특성 기반의 로그 픽셀[3]

그림 3. 3T 기반의 대표적인 logarithmic 픽셀 구조

그림. 3 (a)는 4T-APS 구조에 적용되어 높은 dynamic range 특성을 구현하였다[4]. 로그 센서는 일반적으로 픽셀 구조의 변화 없이 120dB 이상의 높은 dynamic range를 가지는 장점이 있지만, 높은 FPN, 온도에 따른 출력 변화, 색 구현 어려움, 낮은 SNR, 약한 빛에서의 느린 동작 속도의 단점을 가진다. 따라서 로그 센서의 연구는 상기 단점을 개선하는 방향으로 진행됐으며 대표적 연구로는 reference 전류를 이용하여 FPN을 감소시키는 방법[5], 약한 빛에서는 linear, 강한 빛에서는 logarithmic 전압 출력 특성이 있는 방법[4] 등이 있다.

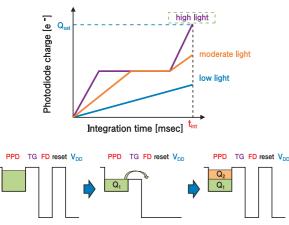

Non-linear 응답을 이용한 다른 HDR 방법으로는 well capacity adjustment 방법이 있다[6]. 이 방법은 앞선 그림 2 (a), (b)의 3T-APS 구조와 4T-APS 구조에서 M1 reset 트랜지스터 게이트의 전압을 integration 시간 동안 펄스 혹은 계단 파형으로 입력하여 HDR을 구현하는 것이다. 다음 그림 4는 well capacity adjustment 방법의 동작 방법을 나타낸 것이다.

그림 4. Well capacity adjustment의 동작 방법

위의 그림 4와 같이 강한 빛이 픽셀에 입사할 경우, 신호가 포화되기 전에 transfer gate(TG)에  $V_{DD}$  보다 낮은 중간 전압 펄스를 인가하여, PPD에는  $Q_1$  전하만 남고 나머지는 전하는 전원( $V_{DD}$ )으로 빠지게 한다. 이어 나머지 짧은 integration 시간 동안 PPD에  $Q_2$  전하를 축척하면 강한 빛에서 포화함이 없이 dynamic range를 증가시킬 수 있다. 이 방법은 픽셀 구조의 변화 없이 간단한 구동을 통하여 100dB 이상의 높은 dynamic range를 가지지만, DR이 높을수록 낮아지는 SNR, SNR 변화(dip) 존재, 높은 FPN 등의 단점을 가진다.

두 개의 민감도(sensitivity)를 가진 포토다이오드(PD)를 이용하여 non-linear 특성의 HDR을 얻는 방법도 있다[7, 8]. 즉, 약한 빛에서는 높은 민감도의 PD를 이용하고 강한 빛에서는 낮은 민감도의 PD를 이용하는 것이다. 대표적 연구로는 PPD와 floating diffusion (FD)를 이용하는 방법[7], 포토게이트(PG)와 n-type 확산 층의 PD를 이용하는 방법[8] 등이 있다. 이 두 방법은 간단한 구동으로

높은 dynamic range를 구현하는 장점이 있지만, reset 잡음이 제거되지 않으며, 전자는 픽셀에 트랜지스터가 추가되며, 후자는 PG의 동작에 의해 큰 FPN을 가지는 단점이 있다.

#### ■ Linear 응답의 HDR 기술

픽셀의 integration 시간이 다른 두 개의 linear 출력 신호를 조합하는 방법을 통해 dynamic range를 향상시킬 수도 있다[9]. 다음 그림 5와 같이, 약한 빛을 감지하기 위해서는 integration 시간을 길게 하고, 강한 빛을 감지하기 위해서는 integration 시간을 짧게 하여 출력 신호가 포화하지 않게 하여, integration 시간이 다른 두 신호를 조합하여 HDR을 구현하는 방법으로 dual sampling 방법이라고도 한다.

그림 5. Dual sampling 방법의 동작범위 확장

이 방법은 픽셀 구조의 변화 없이 100dB 이상의 dynamic range를 가지는 장점이 있지만, 두 개 신호를 처리하기 위한 추가적인 메모 리가 필요하며 integration 시간이 변하는 시점에서의 SNR 변화 (dip)존재, DR이 높을수록 SNR dip이 커지는 문제 등의 단점을 가진다. 따라서 센서의 소형화, 저전력화를 위해서 추가되는 메모리를 제거하는 연구도 지속적으로 진행되어 왔다[10, 11].

또한, SNR dip의 크기를 줄이기 위해서 integration 시간이 다른 세 개 이상의 출력 신호를 얻어 이를 조합하는 방법이 제안되었다 [12]. 하지만 이 방법은 조합하는 세 개 이상의 출력 신호로 말미 암아 메모리가 더 필요하며 고속 동작 회로가 필요하다는 단점을 가진다. Integration 시간 동안 비교기를 이용하여 픽셀 출력 전압 이 어떤 기준 전압 이하가 될 때마다 포토다이오드를 다시 reset하고, reset 되기 전까지의 시간을 저장하여 HDR을 구현하는 방법이 있다[13]. 이는 well capacity의 제한 없이 100dB 정도의 높은 dynamic range를 가지는 장점이 있지만, 픽셀 내의 많은 트랜지 스터의 사용으로 인해서 낮은 fill-factor, 반복되는 reset 동작에 의한 잡음. 비교기의 offset에 의한 큰 FPN의 단점이 있다.

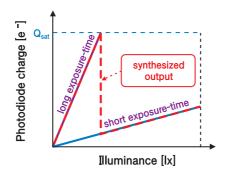

다른 linear 응답의 HDR 방법으로는, 그림 6과 같이 픽셀 안에 추가한 capacitor(CS)를 이용하여 overflow되는 전하를 저장하여 신호의 손실을 없게 하고, well capacitance가 다른 두 출력 신호를 얻은 후 이를 조합하여 HDR을 얻는 방법이 있다[14].

그림 6. 추가된 capacitor(CS)에 의한 HDR 픽셀 구조 [14]

이는 100dB 정도의 높은 dynamic range를 가지는 장점이 있지만, 픽셀 내에 추가된 capacitor(CS)와 트랜지스터(M5)에 의해서 큰 픽셀 크기를 가지는 단점이 있다.

#### 결론

CMOS image sensor(CIS)에서의 high dynamic range (HDR)의 특징과 대표적 기술들을 소개하였다. CIS 기술은 현재 이미지 센서 시장의 대부분을 점유하는 휴대폰 카메라, 디지털카메라, PC 카메라 등의 요구 성능에 맞게 주로 고화질, 고화소, 저가격, 저전력을 중심으로 발전되어 왔다. 한편, 향후 큰 시장 성장이 예견되는 자동차용 카메라는 high dynamic range를 핵심 성능으로 요구하므로, 이를 위한 CIS의 HDR 기술 발전이 앞의 본론에서 살펴보았듯이 광범위하게 진행되고 있다. 앞으로 현재까지 확보된 HDR 기술을 바탕으로 보다 개선이 필요한 화질 열화, 고가격 등의 문제점을 해결하는 방향으로 많은 연구가 진행될 것으로 예상한다.

### Reference

- M.Bigas et al., "Review of CMOS image sensors", Microelectronics J., vol.37, no.5, pp.433-451, May 2006.

- [2] D. Scheffer et al., "Random Addressable 2048 X 2048 Active Pixel Image Sensor", IEEE Trans. Electron Devices, vol.44, no.10, pp.1716–1720, Oct. 1997.

- [3] Y. Ni, and K. Matou, "A CMOS Log Image Sensor with on-chip FPN Compensation", IEEE ESSCIRC, pp.101-104, Sep. 2001.

- [4] K. Hara et al., "A Linear-Logarithmic CMOS Sensor with Offset Calibration Using an Injected Charge Signal", IEEE International Solid-State Circuits Conference, Vol.1 pp.354– 355, February, 2005

- [5] S. Kavadias et al., "A logarithmic response CMOS image sensor with on-chip calibration", IEEE J. Solid-State Circuits, vol.35, no.8, pp.1146-1152, Aug. 2000.

- [6] V. Berezin et al., "Dynamic Range Enlargement in CMOS Imagers with Buried Photodiode", IEEE Workshop on CCDs and Advanced Image Sensors, pp.224-229, May 2003.

- [7] Y. M. Wang et al., "A High Dynamic Range CMOS APS Image Sensor", IEEE Workshop on CCDs and Advanced Image Sensors, pp.137-140, Jun. 2001.

- [8] S. Lee, and K. Yang, "High Dynamic-Range CMOS Image Sensor Cell Based on Self-Adaptive Photosensing Operation", IEEE Trans. Electron Devices, vol. 53, no.7, pp.1733-1735, Jul 2006

- [9] O. Yadid-Pecht, and E. R. Fossum, "Wide Intrascene Dynamic Range CMOS APS Using Dual Sampling", IEEE Trans. Electron Devices, vol.44, no.10, pp.1721-1723, Oct. 1997.

- [10] Y. Egawa et al., "A 1/2.5 inch 5.2Mpixel, 96dB Dynamic Range CMOS Image Sensor with Fixed Pattern Noise Free, Double Exposure Time Read-Out Operation", IEEE ASSCC, pp.135-138, Nov. 2006.

- [11] D. Kim et al., "A Dual-Capture Wide Dynamic Range CMOS Image Sensor Using Floating-Diffusion Capacitor", IEEE Trans. Electron Devices, vol.55, no.10, pp.2590-2594, Oct. 2008

- [12] M. Mase et al., "A Wide Dynamic Range CMOS Image Sensor with Multiple Exposure-Time Signal Outputs and 12-bit Column-Parallel Cyclic A/D Converters", IEEE J. Solid-State Circuits, vol. 40, no.12, pp.2787-2795, Dec. 2005.

- [13] D. Park et al, "A Wide Dynamic-Range CMOS Image Sensor Using Self-Reset Technique", IEEE Electron Device Lett., vol.28, no.10, pp.890-892, Oct. 2007.

- [14] N. Akahane et al., "A Sensitivity and Linearity Improvement of a 100-dB Dynamic Range CMOS Image Sensor Using a Lateral Overflow Integration Capacitor", IEEE J. Solid-State Circuits, vol.41, no.4, pp.851-858, Apr. 2006.